CMOS IC

# SANYO

# LC7152, 7152M, 7152NM, 7152KM

# **Universal Dual-PLL Frequency Synthesizers**

## Overview

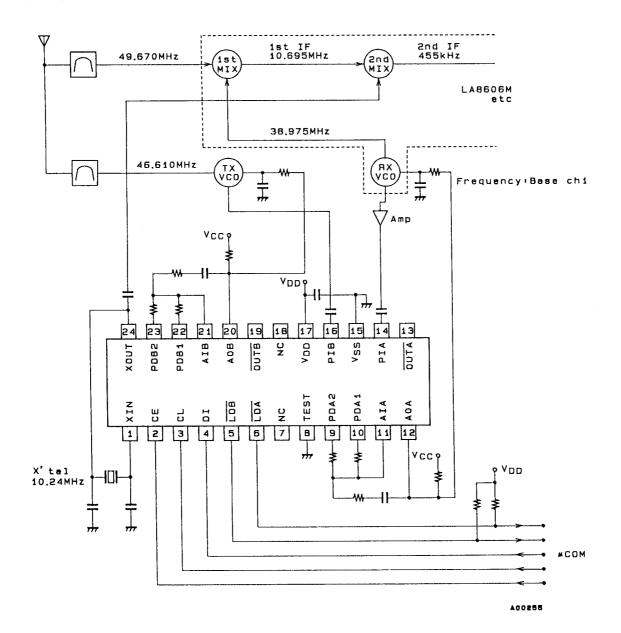

The LC7152, 7152M, 7152NM, 7152KM are universal dual-PLL frequency synthesizers for use in weak signal type cordless telephone applications in the USA, South Korea, and Japan, and broadcast satellite (BS) tuners in the USA and Europe.

# Features

- Dual charge pump built in for fast channel switching

- Digital lock detector enables PLL lock status check with crystal oscillator precision

- Programmable reference frequency divider supports various applications

- The LC7152NM is a built-in power-on reset circuit version of the LC7152M

- The LC7152KM is an enhanced frequency characteristics version of the LC7152M

# Functions

- 2-system PLL built-in (dual PLL)

- 16-bit programmable local-oscillator divider 1.5 to 55 MHz ( $V_{DD}$  = 2.0 to 3.3 V), LC7152KM: 55 to 80 MHz ( $V_{DD}$  = 2.7 to 3.3 V)

- 14-bit programmable reference-frequency divider 320 Hz to 640 kHz reference frequency using a 10.24 MHz crystal oscillator

- · Digital lock detector

- Dual charge pump

- Amplifier built-in for an active LPF

- Serial transmission data input (CCB format)

- LC7152NM with power-on reset circuit (pins OUTA and OUTB become open at power-on)

- 2.0 to 3.3 V supply voltage

- DIP24S and MFP24S packages

CCB is a trademark of SANYO ELECTRIC CO., LTD.

CCB is SANYO's original bus format and all the bus addresses are controlled by SANYO.

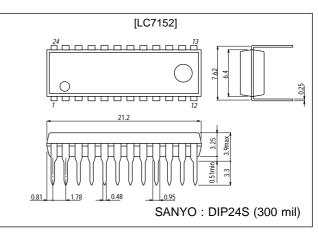

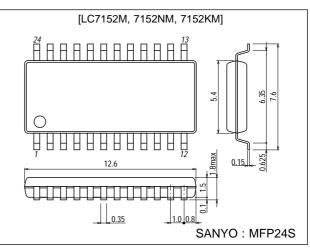

## **Package Dimensions**

unit : mm

### 3067-DIP24S

unit : mm

## 3112-MFP24S

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, operating condition ranges, or other parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co.,Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

# **Specifications**

# Absolute Maximum Ratings at Ta = $25^{\circ}$ C, V<sub>SS</sub> = 0 V

| Parameter                   | Symbol                 | Conditions                          | Ratings                      | Unit |

|-----------------------------|------------------------|-------------------------------------|------------------------------|------|

| Maximum supply voltage      | V <sub>DD</sub> max    | V <sub>DD</sub>                     | -0.3 to +7.0                 | V    |

| Maximum input valtage       | V <sub>IN</sub> max(1) | CE, CL, DI, AIA, AIB                | -0.3 to +7.0                 | V    |

| Maximum input voltage       | V <sub>IN</sub> max(2) | XIN, PIA, PIB, TEST                 | –0.3 to V <sub>DD</sub> +0.3 | V    |

|                             | V <sub>O</sub> max(1)  | LDI, LDB                            | -0.3 to +7.0                 | V    |

| Maximum output voltage      | V <sub>O</sub> max(2)  | AOA, AOB, OUTA, OUTB                | -0.3 to +15                  | V    |

|                             | V <sub>O</sub> max(3)  | PDA1, PDA2, PDB1,<br>PDB2, XOUT     | –0.3 to V <sub>DD</sub> +0.3 | V    |

| Movimum output ourroat      | I <sub>O</sub> max(1)  | LDA, LDB, OUTA, OUTB                | 0 to 3                       | mA   |

| Maximum output current      | I <sub>O</sub> max(2)  | AOA, AOB                            | 0 to 6                       | mA   |

|                             |                        | Ta≦85°C, LC7152                     | 350                          | mW   |

| Allowable power dissipation | Pd max                 | Ta≦85°C, LC7152M,<br>7152NM, 7152KM | 160                          | mW   |

| Operating temperature       | Topr                   |                                     | -40 to +85                   | °C   |

| Storage temperature         | Tstg                   |                                     | -55 to +125                  | °C   |

# Allowable Operating Ranges at Ta = –40 to +85°C, $V_{SS}$ = 0 V

| Deremeter                    | Symbol              | Conditions                                                                   |     | Ratings |      | Unit  |

|------------------------------|---------------------|------------------------------------------------------------------------------|-----|---------|------|-------|

| Parameter                    | Symbol              | Conditions                                                                   | min | typ     | max  | Unit  |

|                              | V <sub>DD</sub> (1) | V <sub>DD</sub>                                                              | 2.0 |         | 3.3  | V     |

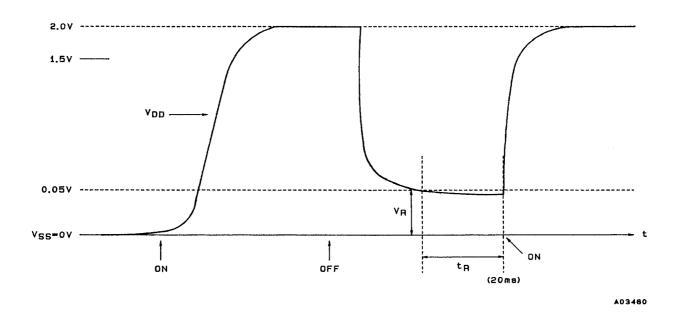

| Supply voltage               | V <sub>DD</sub> (2) | V <sub>DD</sub> :Serial data retention voltage, see Figure1, *1              | 1.5 |         |      | V     |

| oupply voltage               | V <sub>DD</sub> (3) | $V_{DD}$ :Power-on reset voltage, $t_R \geqq 20 \text{ ms},$ see Figure1, *1 |     |         | 0.05 | V     |

| Input high-level voltage     | V <sub>IH</sub> (1) | CE, CL, DI: $V_{DD}$ = 2.0 V                                                 | 1.5 |         | 5.5  | V     |

| input nigh-level voltage     | V <sub>IH</sub> (2) | CE, CL, DI: $V_{DD}$ = 3.3 V                                                 | 1.7 |         | 5.5  | V     |

| Input low-level voltage      | V <sub>IL</sub> (1) | CE, CL, DI: $V_{DD}$ = 2.0 V                                                 | 0   |         | 0.4  | V     |

| input low-level voltage      | V <sub>IL</sub> (2) | CE,CL,DI:V <sub>DD</sub> = 3.3 V                                             | 0   |         | 0.6  | V     |

| Output voltage               | V <sub>O</sub> (1)  | LDA, LDB                                                                     | 0   |         | 5.5  | V     |

| Output voltage               | V <sub>O</sub> (2)  | AOA, AOB, OUTA, OUTB                                                         | 0   |         | 13   | V     |

|                              | f <sub>IN</sub> (1) | XIN:Sine wave, capacitively coupled                                          | 1.0 |         | 13   | MHz   |

| Input frequency              | f <sub>IN</sub> (2) | PIA, PIB: Sine wave, capacitively coupled *2                                 | 1.5 |         | 55   | MHz   |

|                              | f <sub>IN</sub> (3) | PIA, PIB: Sine wave, capacitively coupled *3                                 | 55  |         | 80   | MHz   |

| Input amplitude              | V <sub>IN</sub> (1) | XIN: Sine wave, capacitively coupled                                         | 200 |         | 600  | mVrms |

|                              | V <sub>IN</sub> (2) | PIA, PIB: Sine wave, capacitively coupled *2,3                               | 100 |         | 600  | mVrms |

| Crystal oscillator frequency | f <sub>X'tal</sub>  | XIN, XOUT: CI $\leq$ 50 $\Omega$ CL $\leq$ 16 pF *4                          | 4   | 10.24   | 11   | MHz   |

Note \*1 LC7152NM

|    |                     | FA/FB (serial data inpu | It frequency select bits) | M               | Device                             |

|----|---------------------|-------------------------|---------------------------|-----------------|------------------------------------|

|    |                     | [0]                     | [1]                       | V <sub>DD</sub> | Device                             |

| *2 | f <sub>IN</sub> (2) | 1.5 to 23 MHz           | 20 to 55 MHz              | 2.0 to 3.3 V    | LC7152, 7152M,<br>LC7152NM, 7152KM |

| *3 | f <sub>IN</sub> (3) |                         | 55 to 80 MHz              | 2.7 to 3.3 V    | LC7152KM                           |

\*4 Cl is the crystal impedance and CL is the load capacitance.

| Parameter                     | Symbol               | Conditions                                                                 | Rat                   | ings |      | Unit  |

|-------------------------------|----------------------|----------------------------------------------------------------------------|-----------------------|------|------|-------|

| i diameter                    | Symbol               | Conditions                                                                 | min                   | typ  | max  | Offic |

| Output high-level voltage     | V <sub>OH</sub> (1)  | PDA1, PDB1: I <sub>O</sub> = 1 mA                                          | V <sub>DD</sub> - 1.0 |      |      | V     |

| Suput high-level voltage      | V <sub>OH</sub> (2)  | PDA2, PDB2: $I_0 = 2 \text{ mA}$                                           | V <sub>DD</sub> - 1.0 |      |      | V     |

|                               | V <sub>OL</sub> (1)  | PDA1, PDB1: I <sub>O</sub> 1 mA                                            |                       |      | 1.0  | V     |

|                               | V <sub>OL</sub> (2)  | PDA2, PDB2: I <sub>O</sub> = 2 mA                                          |                       |      | 1.0  | V     |

| Output low-level voltage      | V <sub>OL</sub> (3)  | OUTA, OUTB: I <sub>O</sub> = 1 mA                                          |                       |      | 1.0  | V     |

| Output low-level voltage      | V <sub>OL</sub> (4)  | $\overline{\text{LDA}}, \overline{\text{LDB}}: I_{O} = 2 \text{ mA}$       |                       |      | 1.0  | V     |

|                               | V <sub>OL</sub> (5)  | AOA, AOB: $I_0 = 0.5$ mA, AIA = AIB = 1.2 V                                |                       |      | 0.5  | V     |

|                               | V <sub>OL</sub> (6)  | AOA, AOB: $I_0 = 1 \text{ mA}$ , AIA = AIB = 1.3 V                         |                       |      | 0.5  | V     |

|                               | I <sub>OFF</sub> (1) | $\overline{\text{LDA}}$ . $\overline{\text{LDB}}$ : V <sub>O</sub> = 5.5 V |                       |      | 5.0  | μA    |

| Output off-leakage current    | I <sub>OFF</sub> (2) | PDA1, PDB1, PDA2, PDB2: V <sub>O</sub> = 0/3.3 V                           |                       | 0.01 | 10.0 | nA    |

|                               | I <sub>OFF</sub> (3) | AOA, AOB, $\overline{OUTA}$ , $\overline{OUTB}$ : V <sub>O</sub> = 13 V    |                       |      | 5.0  | μA    |

|                               | I <sub>IH</sub> (1)  | CE, CL, DI: V <sub>I</sub> = 5.5 V                                         |                       |      | 5.0  | μA    |

|                               | I <sub>IH</sub> (2)  | XIN: V <sub>I</sub> = 3.3 V, V <sub>DD</sub> = 3.3 V                       | 2.0                   |      | 6.5  | μA    |

| Input high-level current      | I <sub>IH</sub> (3)  | PIA, PIB: V <sub>I</sub> = 3.3 V, V <sub>DD</sub> = 3.3 V                  | 3.5                   |      | 10.0 | μA    |

|                               | I <sub>IH</sub> (4)  | AIA, AIB: V <sub>1</sub> = 3.3 V                                           |                       | 0.01 | 10.0 | nA    |

|                               | I <sub>IH</sub> (5)  | TEST: V <sub>I</sub> = 3.3 V, V <sub>DD</sub> = 3.3 V                      |                       | 120  |      | μA    |

|                               | I <sub>IL</sub> (1)  | CE, CL, DI: $V_I = 0 V$                                                    |                       |      | 5.0  | μA    |

|                               | I <sub>IL</sub> (2)  | XIN: V <sub>I</sub> = 0 V, V <sub>DD</sub> = 3.3 V                         | 2.0                   |      | 6.5  | μA    |

| Input low-level current       | I <sub>IL</sub> (3)  | PIA, PIB: V <sub>I</sub> = 0 V, V <sub>DD</sub> = 3.3 V                    | 3.5                   |      | 10.0 | μA    |

|                               | I <sub>IL</sub> (4)  | AIA, AIB: $V_1 = 0 V$                                                      |                       | 0.01 | 10.0 | nA    |

|                               | I <sub>IL</sub> (5)  | TEST: V <sub>I</sub> = 0 V, V <sub>DD</sub> = 3.3 V                        |                       |      | 5.0  | μA    |

| Internal feedback resistance  | R <sub>f</sub> (1)   | XIN: $V_{DD} = 3.3 V$                                                      |                       | 1.0  |      | MΩ    |

| Internal reedback resistance  | R <sub>f</sub> (2)   | PIA, PIB:V <sub>DD</sub> = 3.3 V                                           |                       | 600  |      | kΩ    |

| Internal pull-down resistance | Rd                   | TEST: V <sub>DD</sub> = 3.3 V                                              |                       | 30   |      | kΩ    |

| Input capacitance             | C <sub>IN</sub>      | XIN, PIA, PIB                                                              |                       | 2.5  |      | pF    |

| Supply ourroat*1              | I <sub>DD</sub> (1)  | V <sub>DD</sub> (= 2.0 V):f <sub>IN</sub> = 55 MHz                         |                       | 3.0  | 8.0  | mA    |

| Supply current*1              | I <sub>DD</sub> (2)  | V <sub>DD</sub> (= 3.3 V):f <sub>IN</sub> = 55 MHz                         |                       | 7.0  | 14.0 | mA    |

| Current a current #2          | I <sub>DD</sub> (4)  | V <sub>DD</sub> (= 2.0 V):f <sub>IN</sub> = 55 MHz                         |                       | 1.5  | 4.5  | mA    |

| Supply current*2              | I <sub>DD</sub> (5)  | V <sub>DD</sub> (= 3.3 V):f <sub>IN</sub> = 55 MHz                         |                       | 3.9  | 8.0  | mA    |

#### **Electrical Characteristics** in the allowable operating ranges

Note \*1. Dual PLL operation (both PLL-A and PLL-B), SB= 0, XIN= 10.24 MHz (crystal), PIA and PIB input = 100mVrms at f<sub>IN</sub>, all other inputs at V<sub>SS</sub>, all other outputs open.

\*2. Standby mode: Single PLL operation (PLL-A operating and PLL-B stopped), SB = 1, XIN = 10.24 MHz (crystal), PIA input = 100mVrms at  $f_{IN}$ , all other inputs at  $V_{SS}$ , all other outputs open.

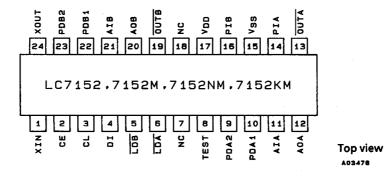

## **Pin Assignment**

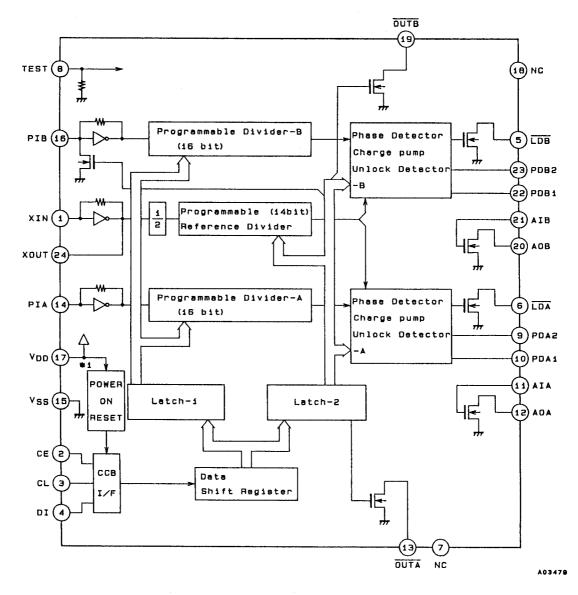

## **Equivalent Block Diagram**

### **Pin Functions**

| Symbol          | Pin No. |                | Function           | Symbol | Pin No. | Function                    |

|-----------------|---------|----------------|--------------------|--------|---------|-----------------------------|

| PIB             | 16      | Side-B oscill  | ator signal input  | PDB2   | 23      | Sub charge pump             |

| XIN             | 1       | Crystal oscill | otor               | PDB1   | 22      | Main charge pump            |

| XOUT            | 24      |                | aloi               | AIB    | 21      | Low-pass filter transistors |

| PIA             | 14      | Side-A oscill  | ator signal output | AOB    | 20      | Low-pass liner transistors  |

| V <sub>DD</sub> | 17      | Power suppl    | у                  | OUTB   | 19      | General-purpose output port |

| V <sub>SS</sub> | 15      | Ground         |                    | LDA    | 6       | Side-A unlock detection     |

| CE              | 2       | Serial data    | Chip enable        | PDA2   | 9       | Sub charge pump             |

| CL              | 3       | input          | Clock              | PDA1   | 10      | Main charge pump            |

| DI              | 4       | linput         | Data               | AIA    | 11      | Low-pass filter transistors |

| TEST            | 8       | IC Test        |                    | AOA    | 12      |                             |

| NC              | 7, 18   | No connection  | ons                | OUTA   | 13      | General-purpose output port |

| LDB             | 5       | Side-B unloc   | k detection        |        |         |                             |

## **Pin Description**

| Symbol                   | Pin No.              | Function                                                                                         |                                                                                                                                                     | Descrip                                                                                                | tion of function                                                                |                                   |

|--------------------------|----------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------|-----------------------------------|

| PIA                      | 14                   | Side-A local oscillator signal                                                                   | Side-A programma                                                                                                                                    | 1                                                                                                      |                                                                                 | ranges are as follows.            |

|                          |                      | input                                                                                            | FA = [0]                                                                                                                                            | FA = [1]                                                                                               | V <sub>DD</sub>                                                                 | Device                            |

|                          |                      |                                                                                                  |                                                                                                                                                     | 20 to 55 MHz                                                                                           | 2.0 to 3.3 V                                                                    | LC7152, 7152M<br>LC7152NM, 7152KM |

|                          |                      |                                                                                                  |                                                                                                                                                     | 55 to 80 MHz                                                                                           | 2.7 to 3.3 V                                                                    | LC7152NM, 7152NM                  |

|                          |                      |                                                                                                  | FA: Serial data                                                                                                                                     | 55 10 00 10112                                                                                         | 2.7 10 5.5 V                                                                    | LOTISZIUM                         |

|                          |                      |                                                                                                  | <ul> <li>Bits DA0 to DA15</li> <li>Divider ratio N =</li> </ul>                                                                                     |                                                                                                        | livider ratios                                                                  |                                   |

| PIB                      | 16                   | Side-B local-oscillator signal                                                                   | <ul> <li>Side-B programma</li> </ul>                                                                                                                |                                                                                                        |                                                                                 |                                   |

| 110                      |                      | input                                                                                            | The input frequence                                                                                                                                 |                                                                                                        | e same as for F                                                                 | 'IA.                              |

|                          |                      |                                                                                                  | $FB(\rightarrow FA)$ : Deter                                                                                                                        | mined by the s                                                                                         | erial data                                                                      |                                   |

|                          |                      |                                                                                                  | Bits DB0 to DB15                                                                                                                                    |                                                                                                        | livider ratios                                                                  |                                   |

|                          |                      |                                                                                                  | Divider ratio N=                                                                                                                                    |                                                                                                        |                                                                                 |                                   |

|                          |                      |                                                                                                  | <ul> <li>Serial data: Bit SB</li> <li>When SB = 1 st</li> </ul>                                                                                     |                                                                                                        |                                                                                 | ndby mode, side-B is              |

|                          |                      |                                                                                                  | stopped, PIB is p                                                                                                                                   |                                                                                                        |                                                                                 | haby mode, side b is              |

|                          |                      |                                                                                                  | When $SB = 0$ , no                                                                                                                                  | ormal operation                                                                                        | is selected.                                                                    |                                   |

| XIN                      | 1                    | Crystal oscillator                                                                               | <ul> <li>Crystal oscillator co</li> </ul>                                                                                                           | · · ·                                                                                                  | '                                                                               | . ,                               |

| XOUT                     | 24                   |                                                                                                  |                                                                                                                                                     |                                                                                                        |                                                                                 | d above, its compatibility        |

|                          | 10                   | Side A main charge nump                                                                          | <ul> <li>With the crys</li> <li>These are PLL characteristics</li> </ul>                                                                            |                                                                                                        | ist be thoroughly                                                               |                                   |

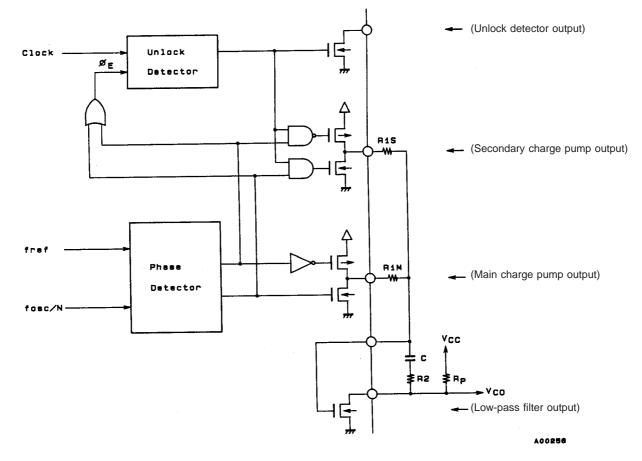

| PDA1                     | 10                   | Side-A main charge pump                                                                          |                                                                                                                                                     |                                                                                                        |                                                                                 | g the local oscillator signal     |

|                          |                      |                                                                                                  |                                                                                                                                                     |                                                                                                        |                                                                                 | ency, the charge pump             |

|                          |                      |                                                                                                  | outputs a high-leve                                                                                                                                 | I signal for the                                                                                       | phase error; wh                                                                 | en lower, the charge pump         |

|                          |                      |                                                                                                  | outputs a low-level                                                                                                                                 | •                                                                                                      |                                                                                 |                                   |

|                          |                      | Cida D main shares sums                                                                          | If the two values m                                                                                                                                 |                                                                                                        | s go to high-imp                                                                | edance.                           |

| PDB1                     | 22                   | Side-B main charge pump                                                                          | • fosc/N > fref or l                                                                                                                                | eading<br>itive Pulse                                                                                  |                                                                                 |                                   |

|                          |                      |                                                                                                  | → Fos<br>• fosc/N < fref or l                                                                                                                       |                                                                                                        |                                                                                 |                                   |

|                          |                      |                                                                                                  |                                                                                                                                                     | ative Pulse                                                                                            |                                                                                 |                                   |

|                          |                      |                                                                                                  | <ul> <li>fosc/N = fref and</li> </ul>                                                                                                               |                                                                                                        |                                                                                 |                                   |

|                          |                      |                                                                                                  |                                                                                                                                                     | n-Impedance                                                                                            |                                                                                 |                                   |

| DDAO                     |                      |                                                                                                  | (*SB = [1] : PDB1 →                                                                                                                                 |                                                                                                        |                                                                                 | ' I I I II                        |

| PDA2                     | 9                    | Side-A sub charge pump                                                                           | <ul> <li>PLL charge pump<br/>unlock condition is</li> </ul>                                                                                         |                                                                                                        | PLL phase error                                                                 | signal only when the              |

|                          |                      |                                                                                                  | <ul> <li>The unlock detection</li> </ul>                                                                                                            |                                                                                                        | set by serial dat                                                               | a bits UL0 and UL1.               |

| PDB2                     | 23                   | Side-B sub charge pump                                                                           |                                                                                                                                                     |                                                                                                        |                                                                                 | tion threshold occurs, this       |

|                          | _                    |                                                                                                  |                                                                                                                                                     |                                                                                                        | d the phase erro                                                                | or signal for the main            |

|                          |                      |                                                                                                  | charge pump is ou                                                                                                                                   |                                                                                                        |                                                                                 |                                   |

|                          |                      |                                                                                                  | <ul> <li>The output pulse o<br/>charge pump.</li> </ul>                                                                                             | f the phase erro                                                                                       | or signal has the                                                               | e same polarity as the main       |

| LDA                      | 6                    | Side-A unlock detector output                                                                    |                                                                                                                                                     | ck/unlock statu                                                                                        | e                                                                               |                                   |

| LDA                      |                      |                                                                                                  | <ul> <li>Outputs the PLL lo<br/>Locked</li> </ul>                                                                                                   |                                                                                                        |                                                                                 |                                   |

|                          |                      |                                                                                                  | Unlocked                                                                                                                                            | •                                                                                                      |                                                                                 |                                   |

|                          |                      |                                                                                                  |                                                                                                                                                     |                                                                                                        | lock/unlock dise                                                                | crimination is set by serial      |

|                          | _                    |                                                                                                  | data bits UL0 and                                                                                                                                   |                                                                                                        |                                                                                 |                                   |

|                          |                      |                                                                                                  |                                                                                                                                                     |                                                                                                        | to and here it is the                                                           |                                   |

| LDB                      | 5                    | Side-B unlock detector output                                                                    |                                                                                                                                                     |                                                                                                        | •                                                                               | data bits UE0 and UE1.            |

| LDB                      | 5                    | Side-B unlock detector output                                                                    | <ul> <li>For details, refer to</li> </ul>                                                                                                           | the description                                                                                        | •                                                                               |                                   |

| AIA                      | 5                    | Side-A low-pass filter transistor                                                                |                                                                                                                                                     | the description                                                                                        | n of the serial da                                                              |                                   |

|                          |                      |                                                                                                  | <ul> <li>For details, refer to</li> <li>SB = 1: LDB → Op</li> <li>MOS N-channel tra</li> </ul>                                                      | the description<br>ben<br>ansistor for the                                                             | n of the serial da                                                              | ta.                               |

| AIA<br>AOA<br>AIB        | 11<br>12<br>21       |                                                                                                  | • For details, refer to<br>• SB = 1: $\overline{\text{LDB}} \rightarrow \text{Op}$                                                                  | the description<br>ben<br>ansistor for the                                                             | n of the serial da                                                              | ta.                               |

| AIA<br>AOA<br>AIB<br>OAB | 11<br>12<br>21<br>20 | Side-A low-pass filter transistor<br>Side-B low-pass filter transistor                           | <ul> <li>For details, refer to</li> <li>SB = 1: LDB → Op</li> <li>MOS N-channel tra</li> <li>The AOA and AOB</li> </ul>                             | o the description<br>pen<br>ansistor for the<br>output withstar                                        | n of the serial da<br>PLL filter<br>nd voltage is 13                            | ta.<br>V.                         |

| AIA<br>AOA<br>AIB        | 11<br>12<br>21       | Side-A low-pass filter transistor<br>Side-B low-pass filter transistor<br>Side-A general purpose | <ul> <li>For details, refer to</li> <li>SB = 1: LDB → Op</li> <li>MOS N-channel tra</li> <li>The AOA and AOB</li> <li>These latch the se</li> </ul> | o the description<br>pen<br>ansistor for the<br>output withstar<br>rial data bits O/                   | n of the serial da<br>PLL filter<br>nd voltage is 13<br>A and OB that an        | ta.                               |

| AIA<br>AOA<br>AIB<br>OAB | 11<br>12<br>21<br>20 | Side-A low-pass filter transistor<br>Side-B low-pass filter transistor                           | <ul> <li>For details, refer to</li> <li>SB = 1: LDB → Op</li> <li>MOS N-channel tra</li> <li>The AOA and AOB</li> </ul>                             | the description<br>pen<br>ansistor for the<br>output withstar<br>rial data bits O/<br>d output the dat | n of the serial da<br>PLL filter<br>Ind voltage is 13<br>A and OB that an<br>a. | ta.<br>V.                         |

For more information on crystal oscillator : Nihon Dempa Kogyo Co., Ltd.

Continued on next page.

Continued from preceding page.

| Symbol                             | Pin No.  | Function               | Description of function                                                                                                                                                                                                                                                                                                        |

|------------------------------------|----------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CE<br>*1                           | 2        | Chip enable input      | • Set this pin high when inputting serial data to the LC7152.                                                                                                                                                                                                                                                                  |

| CL<br>*1                           | 3        | Clock input            | Clock for data synchronization when inputting serial data to the LC7152.                                                                                                                                                                                                                                                       |

| DI<br>*1                           | 4        | Data input             | • Input for serial data being sent from the controller to the LC7152.                                                                                                                                                                                                                                                          |

| V <sub>DD</sub><br>V <sub>SS</sub> | 17<br>15 | Power supply<br>Ground | LC7152 power supply pin.                                                                                                                                                                                                                                                                                                       |

| TEST                               | 8        | IC Test input          | <ul> <li>LC7152 test pin. (Normally V<sub>SS</sub> or open.)</li> <li>However, divide-by-two XIN frequency is output from the pin OUTA by applying the V<sub>DD</sub> level voltage after serial data transfer (T0 = T1 = T2 = 0). Crystal oscillation frequency can be checked normally when the pin is left open.</li> </ul> |

\*1 The input "H" voltage and the input "L" voltage on the CE, CL, and DI pins are  $V_{IH} = 1.5$  to 5.5V and  $V_{IL} = 0$  to 0.4V when  $V_{DD} = 2.0$ V. When  $V_{DD} = 3.3$ V, then  $V_{IH} = 1.7$  to 5.5V and  $V_{IL} = 0$  to 0.6V. (Voltage greater than  $V_{DD}$  may be applied to  $V_{IH}$ .)

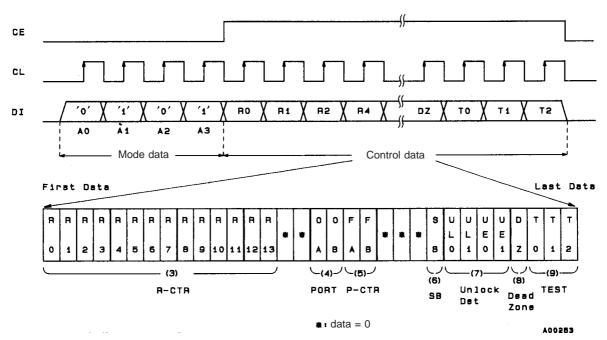

#### Serial Input Data (PLL Control data) format

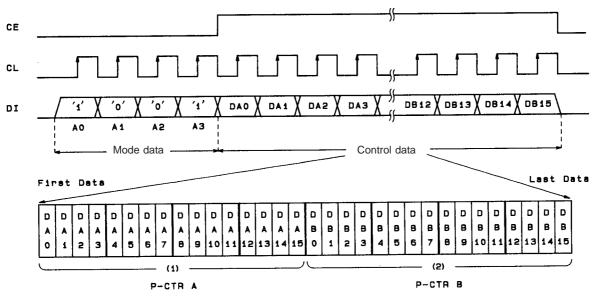

#### Mode1: Latch-1 data (programmable divider data)

A00252

| Symbol          | Parameter                    | 10.24 MHz crystal | Other crystal frequencies     |

|-----------------|------------------------------|-------------------|-------------------------------|

| t <sub>SU</sub> | Data setup time              | At least 0.40 µs  | At least 4/f <sub>X'tal</sub> |

| t <sub>HD</sub> | Data hold time               | At least 0.40 µs  | At least 4/f <sub>X'tal</sub> |

| t <sub>EL</sub> | Enable low-level pulse width | At least 0.40µs   | At least 4/f <sub>X'tal</sub> |

| t <sub>ES</sub> | Enable setup time            | At least 0.40 µs  | At least 4/f <sub>X'tal</sub> |

| t <sub>EH</sub> | Enable hold time             | At least 0.40 µs  | At least 4/f <sub>X'tal</sub> |

| t <sub>CL</sub> | Clock low-level pulse width  | At least 0.40 µs  | At least 4/f <sub>X'tal</sub> |

| <sup>t</sup> CH | Clock high-level pulse width | At least 0.40 µs  | At least 4/f <sub>X'tal</sub> |

| t <sub>LA</sub> | Latch propagation delay      | Up to 0.40 µs     | Up to 4/f <sub>X'tal</sub>    |

Note Perform data transfer after the crystal oscillations normalize. Data transferred before normal oscillations will not be recognized.

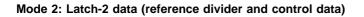

## **Description of Serial Data**

|     | Controller/Data                                        |                                                                                                                             |                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | scription                                                                                                                                                                               |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                             |                                                                                                                                                                | Related Data                |

|-----|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| (1) | Side-A<br>programmable<br>divider data: DA0<br>to DA15 | binary<br>The ra                                                                                                            | value<br>inge o                                                                                                                                                                                                                                | ts the side-A<br>in which DA(<br>f divider value<br>CO-A/fref                                                                                                                                                                                                                                                                                                                                                            | 0 is the LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SB.                                                                                                                                                                                     |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                             | a is a                                                                                                                                                         | R0 to R13                   |

| (2) | Side-B<br>programmable<br>divider data: DB0<br>to DB15 | <ul> <li>This d<br/>binary<br/>The ra</li> </ul>                                                                            | ata se<br>value<br>inge o                                                                                                                                                                                                                      | ts the side-B<br>in which DB(<br>f divider value<br>CO-B/fref                                                                                                                                                                                                                                                                                                                                                            | 0 is the LS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | SB.                                                                                                                                                                                     |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                             | a is a                                                                                                                                                         | R0 to R13                   |

| (3) | Reference<br>frequency data: R0<br>to R13              | which<br>The ra                                                                                                             | R0 is<br>inge o<br>(Actua                                                                                                                                                                                                                      | ts the referer<br>the LSB.<br>f divider value<br>al divider nun<br>ce frequency                                                                                                                                                                                                                                                                                                                                          | es that ca<br>nber) = (se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | n be set i<br>etting) x 2                                                                                                                                                               | is 8 to 16,3<br>2                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                             |                                                                                                                                                                | UL0 UI1 UE0 UE <sup>7</sup> |

| (4) | Output port data:<br>OA, OB                            | • This d<br>O<br>O<br>• Data 0                                                                                              | ata de<br>A $\rightarrow$ C<br>B $\rightarrow$ C<br>): oper                                                                                                                                                                                    | termines the<br>OUTA                                                                                                                                                                                                                                                                                                                                                                                                     | output on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | the gene                                                                                                                                                                                | eral-purpos                                                                                                                                                                                                                                                              | e output p                                                                                                                                                                                                                  | ort.                                                                                                                                                           |                             |

| (5) | Input frequency<br>range switching<br>data: FA, FB     | (FA →                                                                                                                       |                                                                                                                                                                                                                                                | ritches the inp<br>$FB \rightarrow PIB$ )<br>Data<br>[0]<br>[1]<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data<br>Data                                                                                                                                                                                                                          | Supply v<br>2.0<br>1.5 t<br>20 to                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | voltage (\<br>to 3.3 V<br>to 23 MHz<br>o 55 MHz                                                                                                                                         | / <sub>DD</sub> )<br>z                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                             |                                                                                                                                                                | DA0 to DA15<br>DB0 to DB15  |

| (6) | Standby mode data<br>: SB                              | • This d<br>• Sl                                                                                                            | ata pu<br>B = 1:<br>→ S<br>B = 0:                                                                                                                                                                                                              | ts the PLL in<br>standby moc<br>ingle PLL op<br>standby moc<br>pual PLL oper                                                                                                                                                                                                                                                                                                                                             | standby r<br>de (LDB pi<br>eration: Si<br>de off                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | mode.<br>in: open)<br>ide-A ope                                                                                                                                                         | rating, side                                                                                                                                                                                                                                                             | e-B stoppe                                                                                                                                                                                                                  | d                                                                                                                                                              |                             |