DT28F016SA-100 查看數據表(PDF) - Intel

零件编号

产品描述 (功能)

生产厂家

DT28F016SA-100 Datasheet PDF : 55 Pages

| |||

28F016SA

E

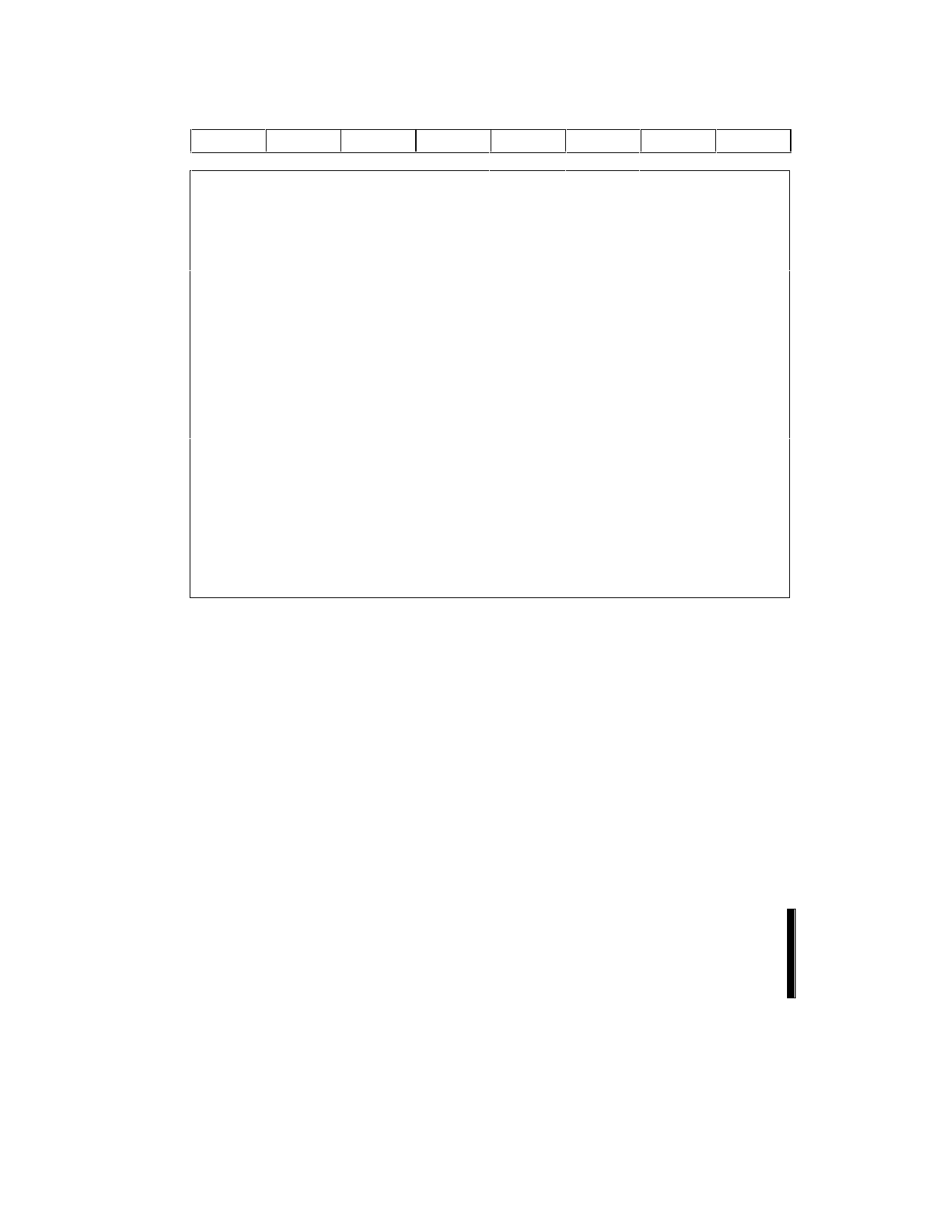

4.5 Compatible Status Register

WSMS

ESS

ES

DWS

VPPS

R

R

R

7

6

5

4

3

2

1

0

CSR.7 = WRITE STATE MACHINE STATUS

1 = Ready

0 = Busy

NOTES:

RY/BY# output or WSMS bit must be checked to

determine completion of an operation (erase

suspend, block erase or data program) before the

appropriate Status bit (ESS, ES or DWS) is

checked for success.

CSR.6 = ERASE-SUSPEND STATUS

1 = Erase Suspended

0 = Erase In Progress/Completed

CSR.5 = ERASE STATUS

1 = Error In Block Erasure

0 = Successful Block Erase

If DWS and ES are set to “1” during a block

erase attempt, an improper command sequence

was entered. Clear the CSR and attempt the

operation again.

CSR.4 = DATA WRITE STATUS

1 = Error in Data Program

0 = Data Program Successful

CSR.3 = VPP STATUS

1 = VPP Low Detect, Operation Abort

0 = VPP OK

The VPPS bit, unlike an A/D converter, does not

provide continuous indication of VPP level. The

WSM interrogates VPP’s level only after the Data

Program or Block Erase command sequences

have been entered, and informs the system if

VPP has not been switched on. VPPS is not

guaranteed to report accurate feedback between

VPPL and VPPH.

CSR.2–0 = RESERVED FOR FUTURE ENHANCEMENTS

These bits are reserved for future use; mask them out when polling the CSR.

18