VSC7216-01 查看數據表(PDF) - Vitesse Semiconductor

零件编号

产品描述 (功能)

生产厂家

VSC7216-01 Datasheet PDF : 38 Pages

| |||

VITESSE

SEMICONDUCTOR CORPORATION

Preliminary Datasheet

VSC7216-01

Multi-Gigabit Interconnect Chip

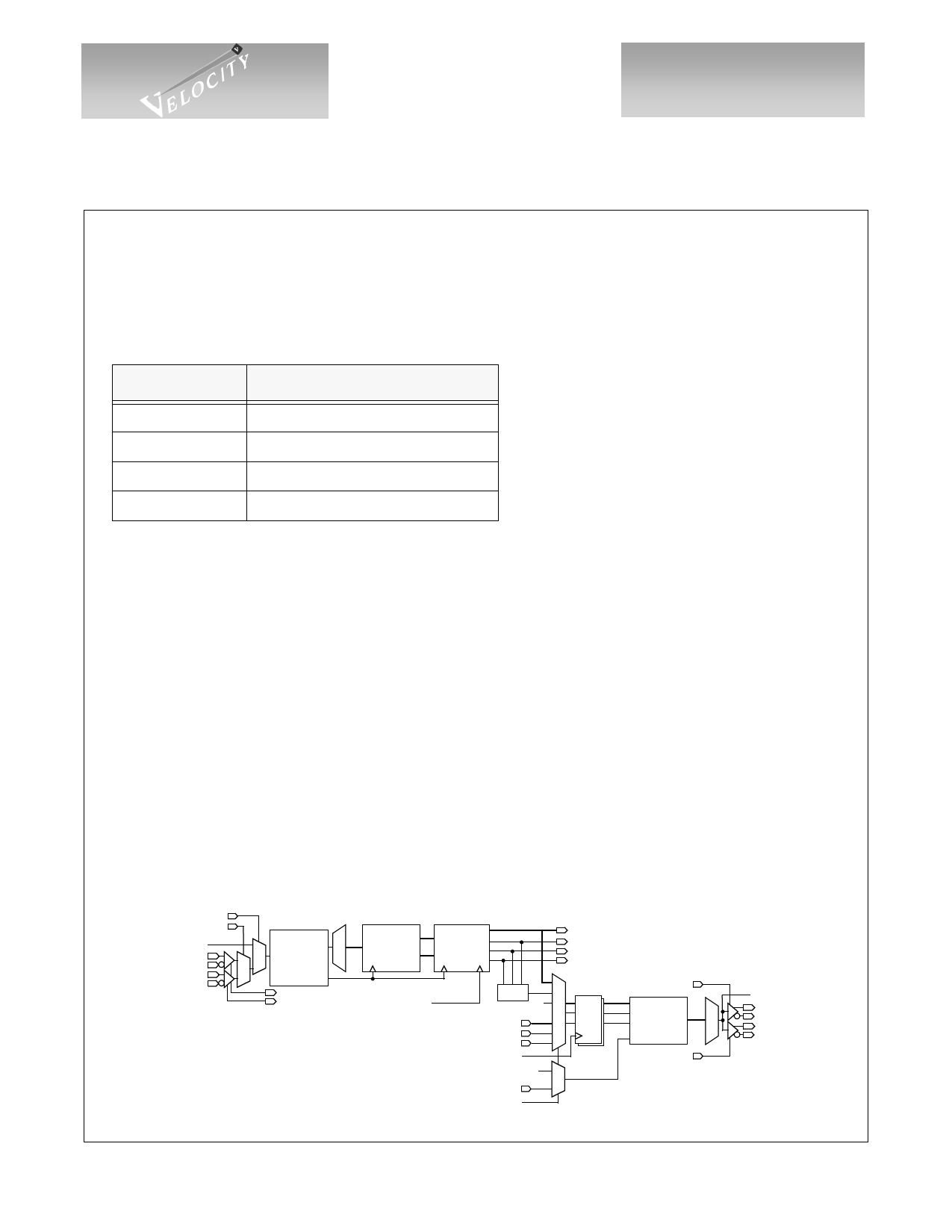

Loopback Operation

Loop back control pins, LBENn(1:0), are provided in each channel to internally loopback data paths for on-

chip diagnosis. Both serial and parallel loopback functions are provided.

Table 9: Loopback Mode Selection

LBENn(1:0)

00

01

10

11

Loopback Mode

Normal Operation

Internal Parallel Loopback

Internal Serial Loopback

Reserved

When LBENn(1:0)=10, Serial Loopback mode is selected, the transmitter’s serial transmit data is internally

connected to the receiver’s CRU input. The serial loopback paths are labeled LBTXn in the VSC7216-01 block

diagram on the first page. This allows parallel data on Tn(7:0) to be encoded, serialized, looped back,

deserialized and decoded. This mode is intended for the system to verify functionality of the local VSC7216-01

prior to attempting to establish an external link. The PTXn and RTXn outputs are unaffected by the state of

LBENn(1:0).

When LBENn(1:0)=01, Parallel Loopback mode is selected. The Rn(7:0) outputs are looped back to the

Tn(7:0) inputs (Figure 11). WSENn does not have a loopback source and is internally connected to a logic

LOW. KCHAR does not have a loopback source and is internally connected to a logic HIGH. The C/Dn input is

obtained by decoding the link status outputs such that either a data character, special character, or IDLE (K28.5)

is transmitted. When the link is in the LOS or RESYNC states, C/Dn is asserted and the data path is set to 0xBC

so that an IDLE will be transmitted. For other link status conditions C/Dn follows the KCHn status bit. This

guarantees that IDLE and special characters will be correctly looped back along with normal data, and also has

the effect of looping back the data received as a normal data character when a disparity error, out-of-band

character, or underflow/overflow link status condition occurs.

LBENn(1:0)

RXP/Rn

LBTXn

PRXn+

PRXn-

RRXn+

RRXn-

Figure 11: Parallel Loopback Mode Operation

Clk/Data

Recovery

8

10 8B/10B 8 Elastic

Decode 3 Buffer

Rn(7:0)

IDLEn

KCHn

ERRn

PSDETn

RSDETn

ªREFCLK

RECEIVER

(dec)

1

0

Tn(7:0)

8

C/Dn

0

WSENn

ªREFCLK

11

KCHAR

0

PARLOOP

8

DQ

PTXENn

8B/10B 10

Encode

RTXENn

LBTXn

PTXn+

PTXn-

RTXn+

RTXn-

TRANSMITTER

G52352-0, Rev 3.2

05/05/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 17