74AHC273PWDH 查看數據表(PDF) - Philips Electronics

零件编号

产品描述 (功能)

生产厂家

74AHC273PWDH Datasheet PDF : 20 Pages

| |||

Philips Semiconductors

Octal D-type flip-flop with reset;

positive-edge trigger

Product specification

74AHC273; 74AHCT273

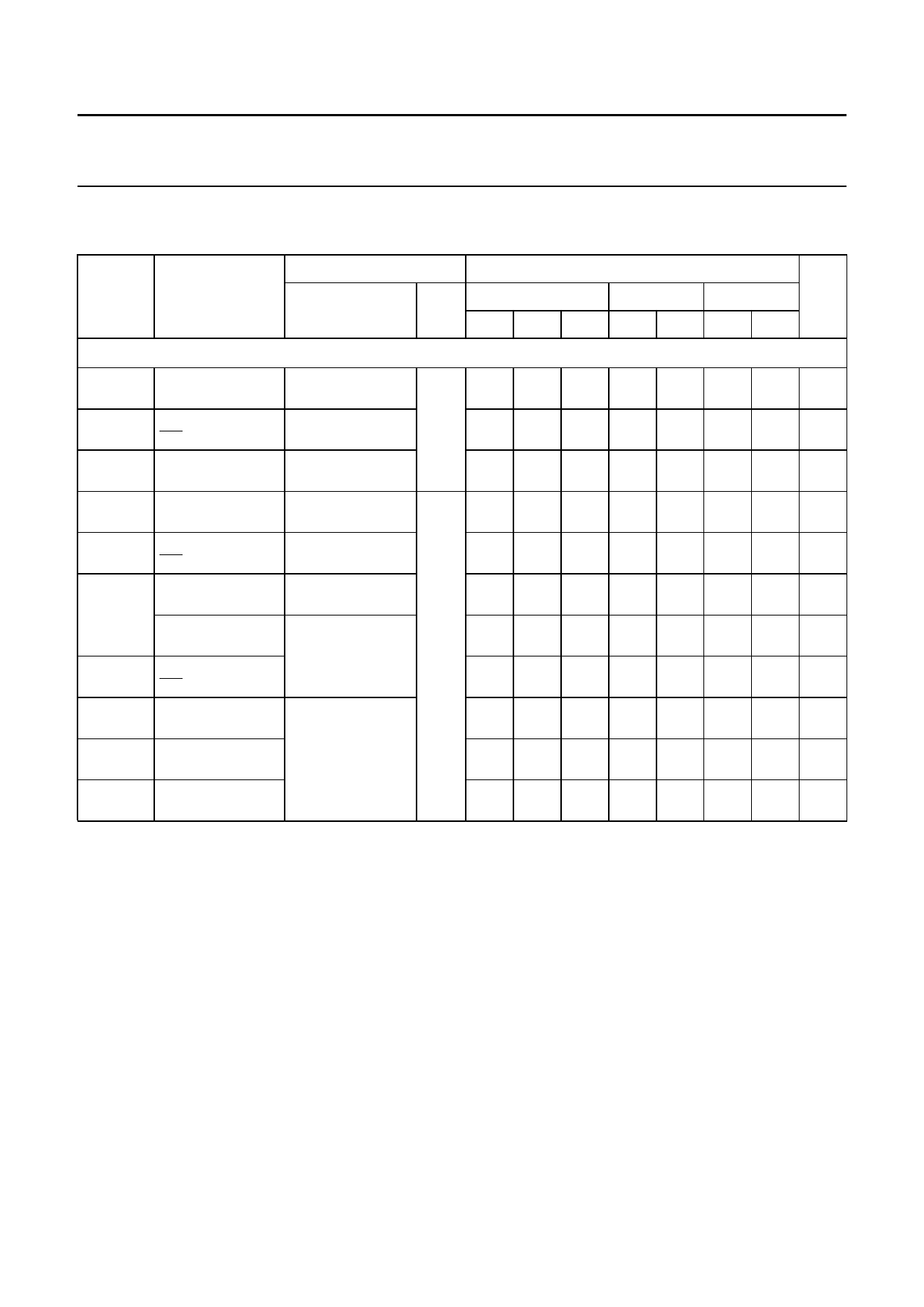

Type 74AHCT273

Ground = 0 V; tr = tf ≤ 3.0 ns.

SYMBOL

PARAMETER

TEST CONDITIONS

WAVEFORMS

CL

Tamb (°C)

25

−40 to +85 −40 to +125 UNIT

MIN. TYP. MAX. MIN. MAX. MIN. MAX.

VCC = 4.5 to 5.5 V; note 1

tPHL/tPLH

tPHL

fmax

propagation delay

CP to Qn

propagation delay

MR to Qn

maximum clock

pulse frequency

see Figs 6 and 9

see Figs 7 and 9

tPHL/tPLH

tPHL

tW

propagation delay

CP to Qn

propagation delay

MR to Qn

clock pulse width

HIGH or LOW

see Figs 6 and 9

see Figs 7 and 9

see Figs 6 and 9

master reset

see Figs 7 and 9

pulse width LOW

trem

removal time

MR to CP

tsu

setup time

see Figs 8 and 9

Dn to CP

th

hold time

Dn to CP

fmax

maximum clock

pulse frequency

15 pF −

−

75

50 pF −

−

5.0

5.0

2.5

3.0

1.0

50

4.0 7.5 1.0

3.9 10.0 1.0

120 −

65

5.8 9.2 1.0

5.6 11.0 1.0

−

−

6.5

−

−

6.0

−

−

2.5

−

−

3.0

−

−

1.0

75 −

45

8.8 1.0

11.6 1.0

−

65

10.5 1.0

12.6 1.0

−

6.5

−

6.0

−

2.5

−

3.0

−

1.0

−

45

9.5 ns

12.5 ns

−

ns

11.5 ns

14.0 ns

−

ns

−

ns

−

ns

−

ns

−

ns

−

ns

Note

1. Typical values at VCC = 5.0 V.

1999 Sep 01

11