A25L10P 查看數據表(PDF) - AMIC Technology

零件编号

产品描述 (功能)

生产厂家

A25L10P

A25L10P Datasheet PDF : 43 Pages

| |||

Bulk Erase (BE)

The Bulk Erase (BE) instruction sets all bits to 1 (FFh). Before

it can be accepted, a Write Enable (WREN) instruction must

previously have been executed. After the Write Enable

(WREN) instruction has been decoded, the device sets the

Write Enable Latch (WEL).

The Bulk Erase (BE) instruction is entered by driving Chip

Select ( S ) Low, followed by the instruction code on Serial

Data Input (DIO). Chip Select ( S ) must be driven Low for the

entire duration of the sequence.

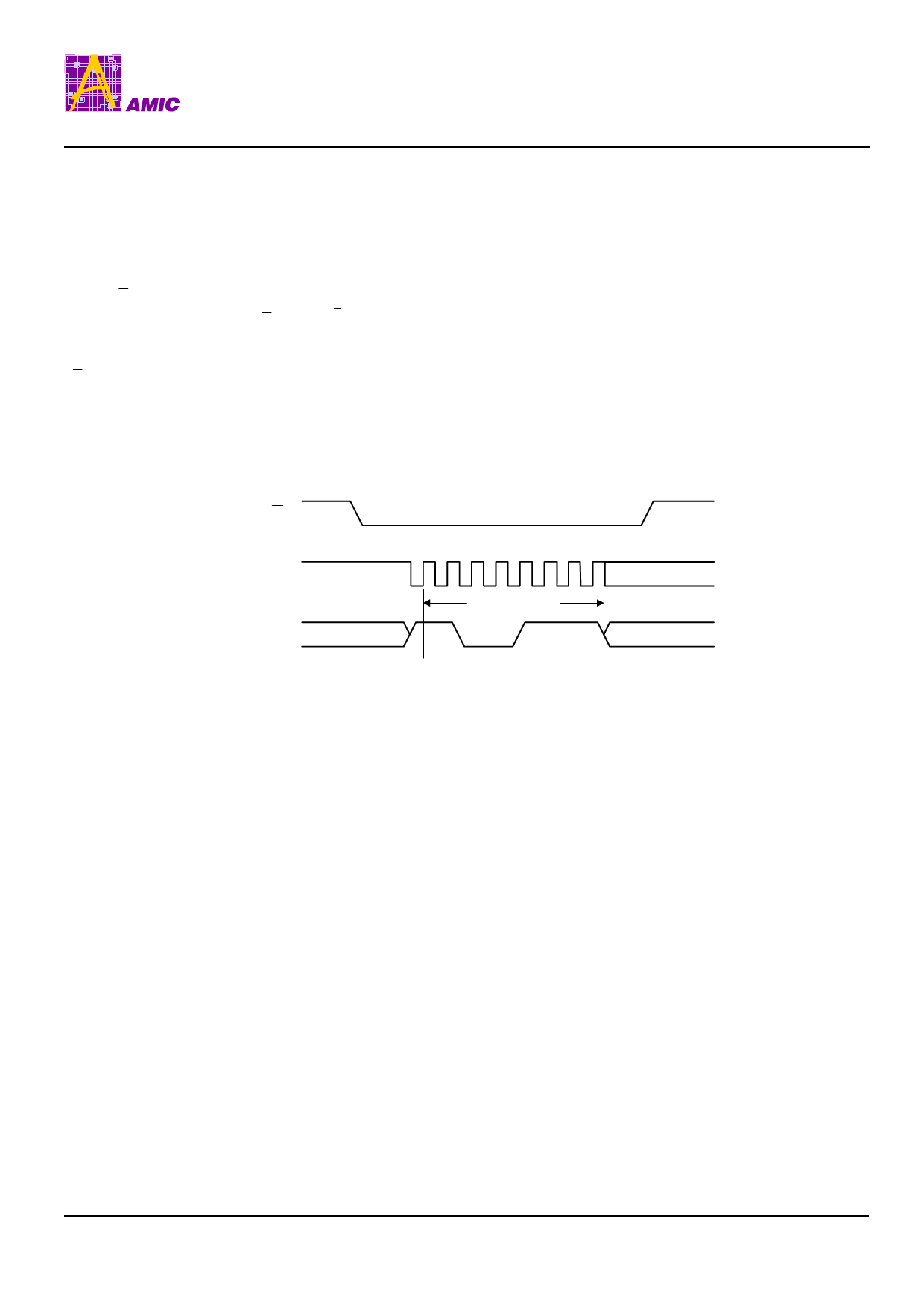

The instruction sequence is shown in Figure 14. Chip Select

( S ) must be driven High after the eighth bit of the instruction

code has been latched in, otherwise the Bulk Erase instruction

Figure 14. Bulk Erase (BE) Instruction Sequence

A25L20P/A25L10P/A25L05P Series

is not executed. As soon as Chip Select ( S ) is driven High,

the self-timed Bulk Erase cycle (whose duration is tBE) is

initiated. While the Bulk Erase cycle is in progress, the Status

Register may be read to check the value of the Write In

Progress (WIP) bit. The Write In Progress (WIP) bit is 1 during

the self-timed Bulk Erase cycle, and is 0 when it is completed.

At some unspecified time before the cycle is completed, the

Write Enable Latch (WEL) bit is reset.

The Bulk Erase (BE) instruction is executed only if all Block

Protect (BP1, BP0) bits are 0. The Bulk Erase (BE) instruction

is ignored if one, or more, sectors are protected.

S

01 2 3 45 67

C

Instruction

DIO

Note: Address bits A23 to A18 are Don’t Care, for A25L20P.

Address bits A23 to A17 are Don’t Care, for A25L10P.

Address bits A23 to A16 are Don’t Care, for A25L05P

(August, 2007, Version 1.0)

22

AMIC Technology Corp.