AS3930 查看數據表(PDF) - austriamicrosystems AG

零件编号

产品描述 (功能)

生产厂家

AS3930 Datasheet PDF : 32 Pages

| |||

AS3930

Datasheet - Detailed Description

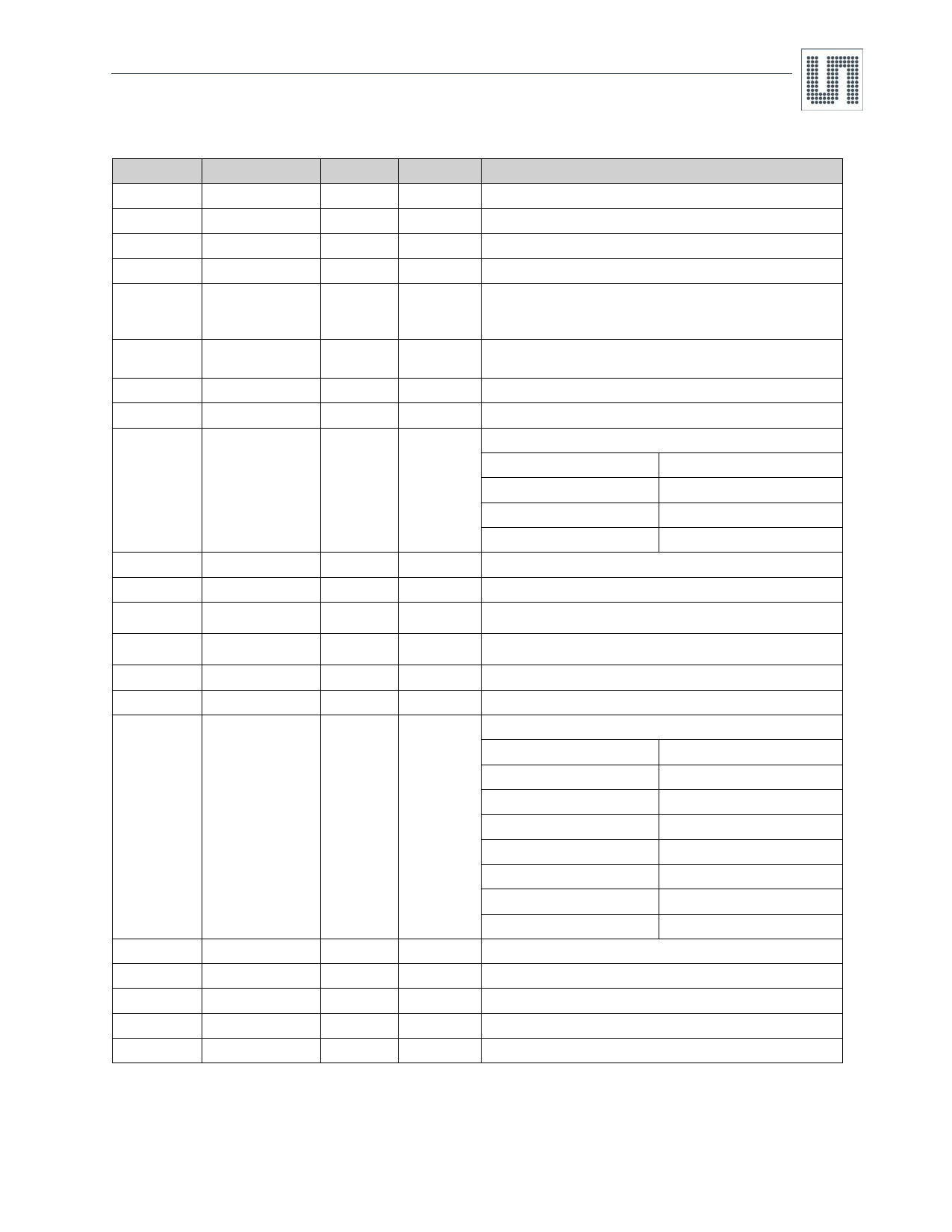

Table 7. Description and Default Values

Register

R2<7>

R2<6:5>

Name

S_ABSH

W_PAT

Type Default Value

Description

R/W

0

Data slicer threshold reduction

R/W

00

Pattern correlation tolerance (see Table 20)

R2<4:2>

R2<1:0>

Reserved

S_WU1

000

Reserved

R/W

00

Tolerance setting for the stage wake-up (see Table 14)

Data slicer hysteresis

R3<7>

HY_20m

R/W

0

if HY_20m = 0, then comparator hysteresis = 40mV

if HY_20m = 1, then comparator hysteresis = 20mV

R3<6>

R3<5:3>

HY_POS

FS_SCL

R/W

0

Data slicer hysteresis on both edges (HY_POS=0 → hysteresis on

both edges; HY_POS=1 → hysteresis only on positive edges)

R/W

100

Data slicer time constant (see Table 18)

R3<2:0>

FS_ENV

R/W

000

Envelop detector time constant (see Table 17)

Off time in ON/OFF operation mode

T_OFF=00

1ms

R4<7:6>

T_OFF

R/W

00

T_OFF=01

2ms

T_OFF=10

4ms

R4<5:4>

D_RES

T_OFF=11

8ms

R/W

01

Antenna damping resistor (see Table 16)

R4<3:0>

GR

R/W

0000 Gain reduction (see Table 15)

R5<7:0>

TS2

R/W

01101001 2nd Byte of wake-up pattern

R6<7:0>

R7<7:5>

R7<4:0>

TS1

T_OUT

T_HBIT

R/W

10010110 1st Byte of wake-up pattern

R/W

000

Automatic time-out (see Table 21)

R/W

01011 Bit rate definition (see Table 19)

Artificial wake-up

T_AUTO=000

No artificial wake-up

T_AUTO=001

1 sec

R8<2:0>

T_AUTO

R/W

000

T_AUTO=010

T_AUTO=011

5 sec

20 sec

T_AUTO=100

2 min

T_AUTO=101

15 min

T_AUTO=110

1 hour

R9<6:0>

Reserved

000000

T_AUTO=111

Reserved

2 hour

R10<4:0>

RSSI

R

R11<4:0>

R

RSSI channel

n.a.

R12<4:0>

R

R13<7:0>

F_WAK

R

n.a.

False wake-up register

www.ams.com/LF-Receiver/AS3930

Revision 1.5

13 - 32