A80960CF-40 查看數據表(PDF) - Intel

零件编号

产品描述 (功能)

生产厂家

A80960CF-40 Datasheet PDF : 77 Pages

| |||

80960CF-40, -33, -25, -16

A

Name

HOLDA

BREQ

D/C

DMA

SUP

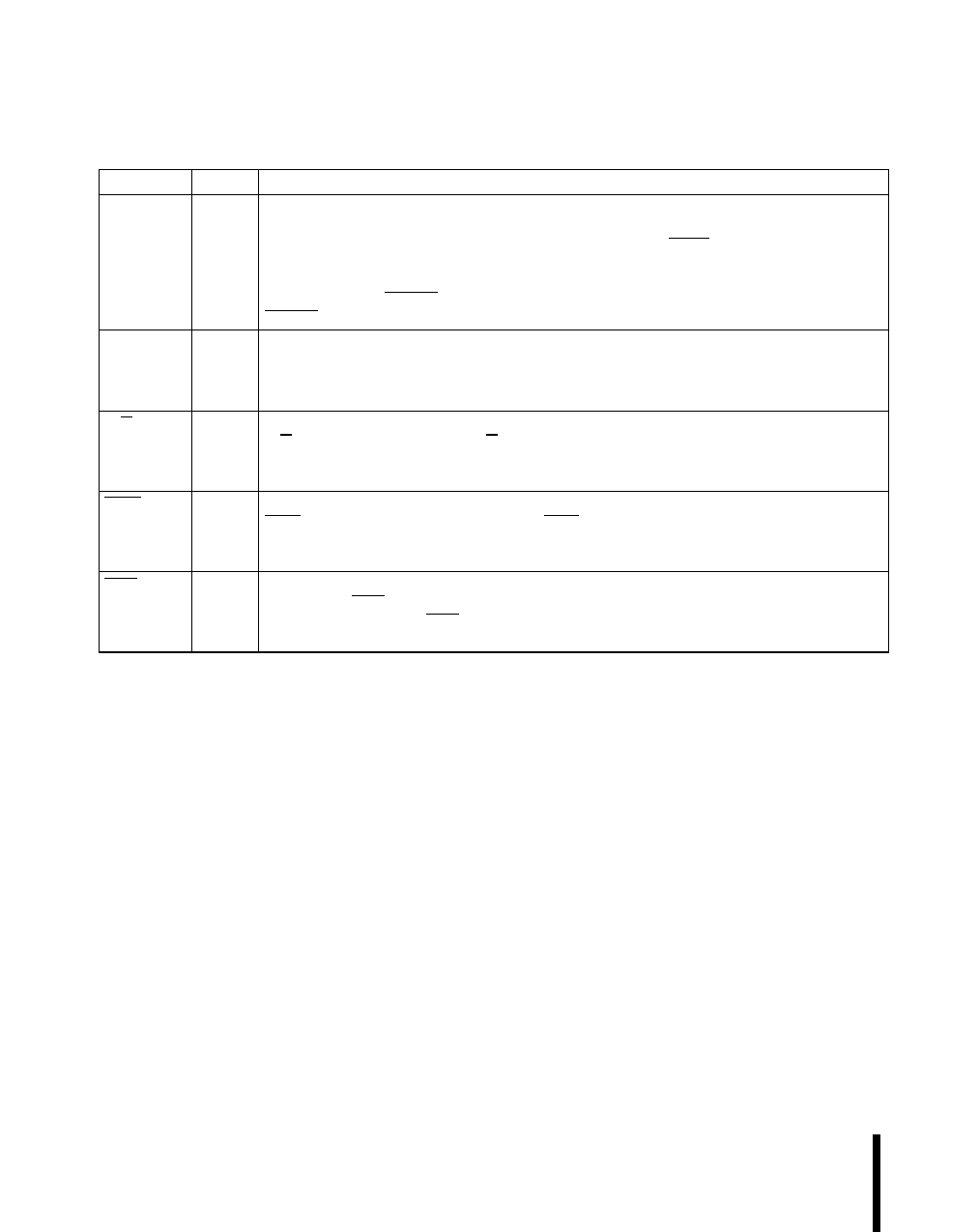

Table 2. 80960CF Pin Description — External Bus Signals (Sheet 3 of 3)

Type

O

S

H(1)

R(Q)

O

S

H(Q)

R(0)

O

S

H(Z)

R(Z)

O

S

H(Z)

R(Z)

O

S

H(Z)

R(Z)

Description

HOLD ACKNOWLEDGE indicates to a bus requestor that the processor has relin-

quished control of the external bus. When HOLDA is asserted, the external address

bus, data bus and bus control signals are floated. HOLD, BOFF, HOLDA and BREQ are

used together to arbitrate access to the processor’s external bus by external bus

agents. Since the processor grants HOLD requests and enters the Hold Acknowledge

state even while RESET is asserted, the state of the HOLDA pin is independent of the

RESET pin.

BUS REQUEST is asserted when the bus controller has a request pending. BREQ can

be used by external bus arbitration logic in conjunction with HOLD and HOLDA to deter-

mine when to return mastership of the external bus to the processor.

DATA OR CODE is asserted for a data request and deasserted for instruction requests.

D/C has the same timing as W/R.

DMA ACCESS indicates whether the bus request was initiated by the DMA controller.

DMA is asserted for any DMA request. DMA is deasserted for all other requests.

SUPERVISOR ACCESS indicates whether the bus request is issued while in super-

visor mode. SUP is asserted when the request has supervisor privileges and is

deasserted otherwise. SUP can be used to isolate supervisor code and data structures

from non-supervisor requests.

8

PRELIMINARY