MSM6222 查看數據表(PDF) - Oki Electric Industry

零件编号

产品描述 (功能)

生产厂家

MSM6222

MSM6222 Datasheet PDF : 45 Pages

| |||

¡ Semiconductor

MSM6222B-xx

FUNCTIONAL DESCRIPTION

Instruction Register (IR) and Data Register (DR)

These two registers are selected by the REGISTER SELECTOR (RS) pin.

The DR is selected when the "H" level is input to the RS pin and IR is selected when the "L"

level is input.

The IR is used to store the address of the display data RAM (DD RAM) or character

generator RAM (CG RAM) and instruction code.

The IR can be written, but not be read by the microcomputer (CPU).

The DR is used to write and read the data to and from the DD RAM or CG RAM.

The data written to DR by the CPU is automatically written to the DD RAM or CG RAM

as an internal operation.

When an address code is written to IR, the data (of the specified address) is automatically

transferred from the DD RAM or CG RAM to the DR. Next, when the CPU reads the DR,

it is possible to verify DD RAM or CG RAM data from the DR data.

After the writing of DR by the CPU, the next adress in the DD RAM or CG RAM is selected

to be ready for the next CPU writing.

Likewise, after the reading out of DR by the CPU, DD RAM or CG RAM data is read out

by the DR to be ready for the next CPU reading.

Write/read to and from both registers is carried out by the READ/WRITE (R/W) pin.

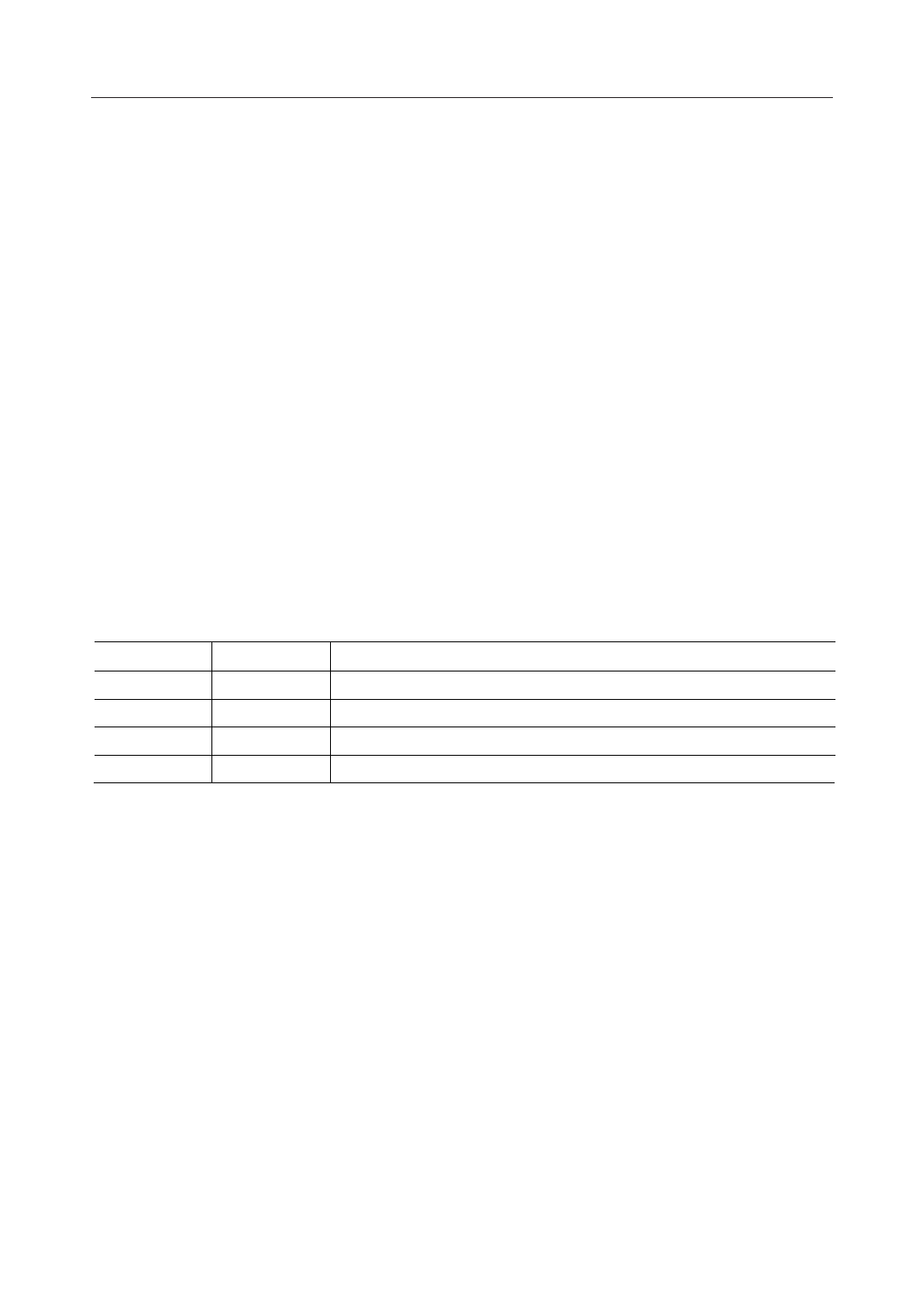

Table 1 RS and R/W pins functions

R/W

RS

Function

L

L

IR write

H

L

Read of busy flag (BF) and address counter (ADC)

L

H

DR write

H

H

DR read

Busy Flag (BF)

When the busy flag is at "H", it indicates that the MSM6222B-xx is engaged in internal

operation.

When the busy flag is at "H", any new instruction is ignored.

When R/W = "H" and RS = "L", the busy flag is output from DB7.

New instruction should be input when busy flag is "L" level.

When the busy flag is at "H", the output code of the address counter (ADC) is undefined.

Address Counter (ADC)

The address counter (ADC) allocates the address for the DD RAM and CG RAM write/read

and also for the cursor display.

When the instruction code for a DD RAM address or CG RAM address setting is input to IR,

after deciding whether it is DD RAM or CG RAM, the address code is transferred from IR

to ADC. After writing (reading) the display data to (from) the DD RAM or CG RAM, the

ADC is incremented (decremented) by 1 internally.

The data of the ADC is output to DB0 - DB6 on the conditions that R/W = "H", RS = "L", and

BF = "L".

13/45