LM4040AIX3-2.5T(2019) 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

LM4040AIX3-2.5T

(Rev.:2019)

(Rev.:2019)

LM4040AIX3-2.5T Datasheet PDF : 17 Pages

| |||

LM4040

Improved Precision Micropower Shunt Voltage

Reference with Multiple Reverse Breakdown Voltages

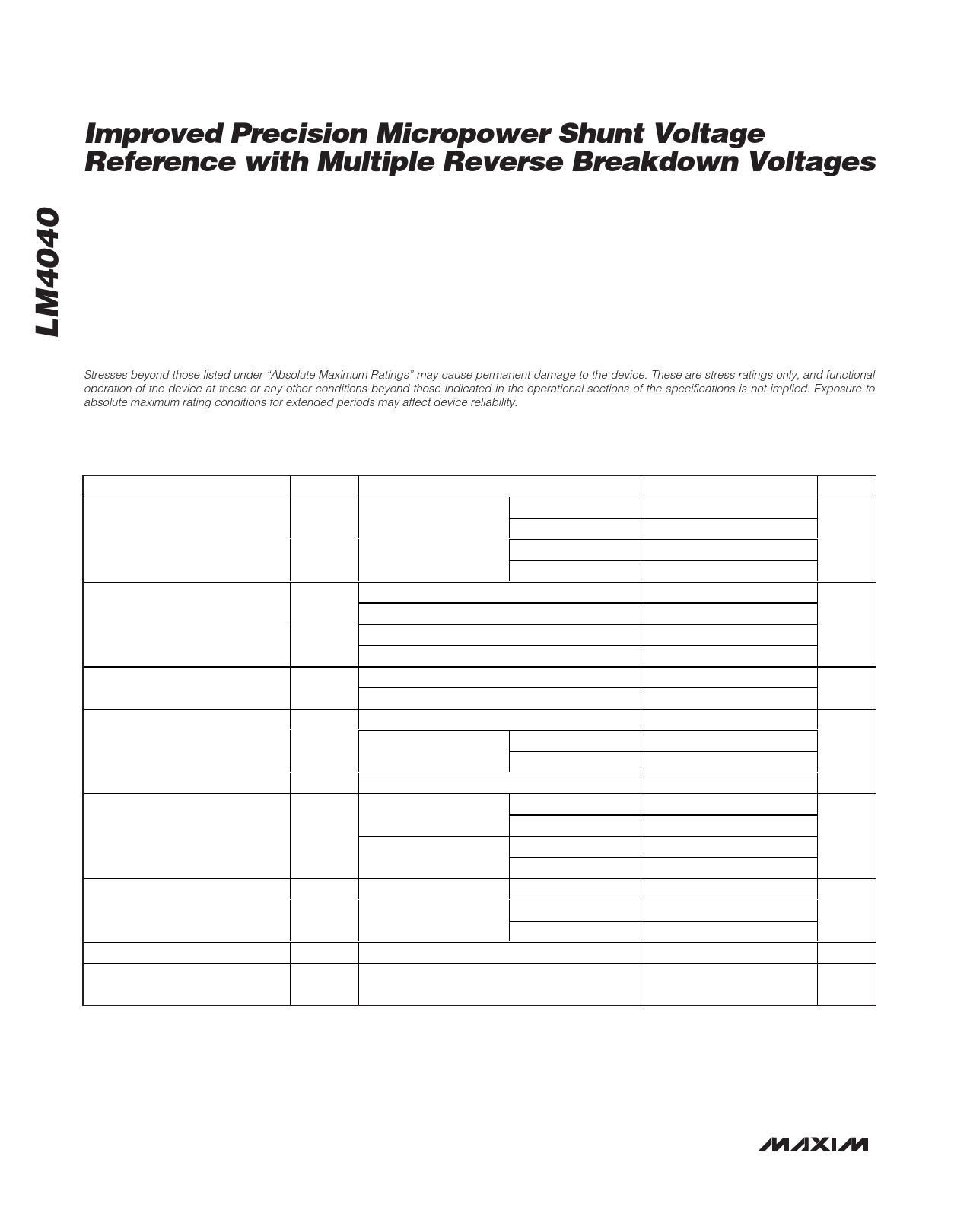

Absolute Maximum Ratings

Reverse Current (cathode to anode)..................................20mA

Forward Current (anode to cathode)...................................10mA

Continuous Power Dissipation (TA = +70°C)

3-Pin SC70 (derate 2.90mW/°C above +70°C)............235mW

3-Pin SOT23 (derate 3mW/°C above +70°C)...........238.1mW

Operating Temperature Range

LM4040_I_ _ _................................................ -40°C to +85°C

LM4040_E_ _ _............................................. -40°C to +125°C

Storage Temperature Range............................. -65°C to +150°C

Junction Temperature.......................................................+150°C

Lead Temperature (soldering, 10s).................................. +300°C

Soldering Temperature (reflow)........................................ +260°C

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these

or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

device reliability.

Package Information

3 SOT23

PACKAGE CODE

Outline Number

Land Pattern Number

Thermal Resistance, Single-Layer Board:

Junction to Ambient (θJA)

Junction to Case (θJC)

Thermal Resistance, Four-Layer Board:

Junction to Ambient (θJA)

Junction to Case (θJC)

3 SC70

21-0051

90-0179

N/A

N/A

336°C/W

110.10°C/W

U3+1

PACKAGE CODE

Outline Number

Land Pattern Number

Thermal Resistance, Single-Layer Board:

Junction to Ambient (θJA)

Junction to Case (θJC)

Thermal Resistance, Four-Layer Board:

Junction to Ambient (θJA)

Junction to Case (θJC)

21-0075

90-0208

340°C/W

115°C/W

340.40°C/W

120°C/W

X3+2

For the latest package outline information and land patterns (footprints), go to www.maximintegrated.com/packages. Note that a “+”,

“#”, or “-” in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing

pertains to the package regardless of RoHS status.

Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board.

For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

www.maximintegrated.com

Maxim Integrated │ 2