EN80960SA 查看數據表(PDF) - Intel

零件编号

产品描述 (功能)

生产厂家

EN80960SA Datasheet PDF : 39 Pages

| |||

80960SA

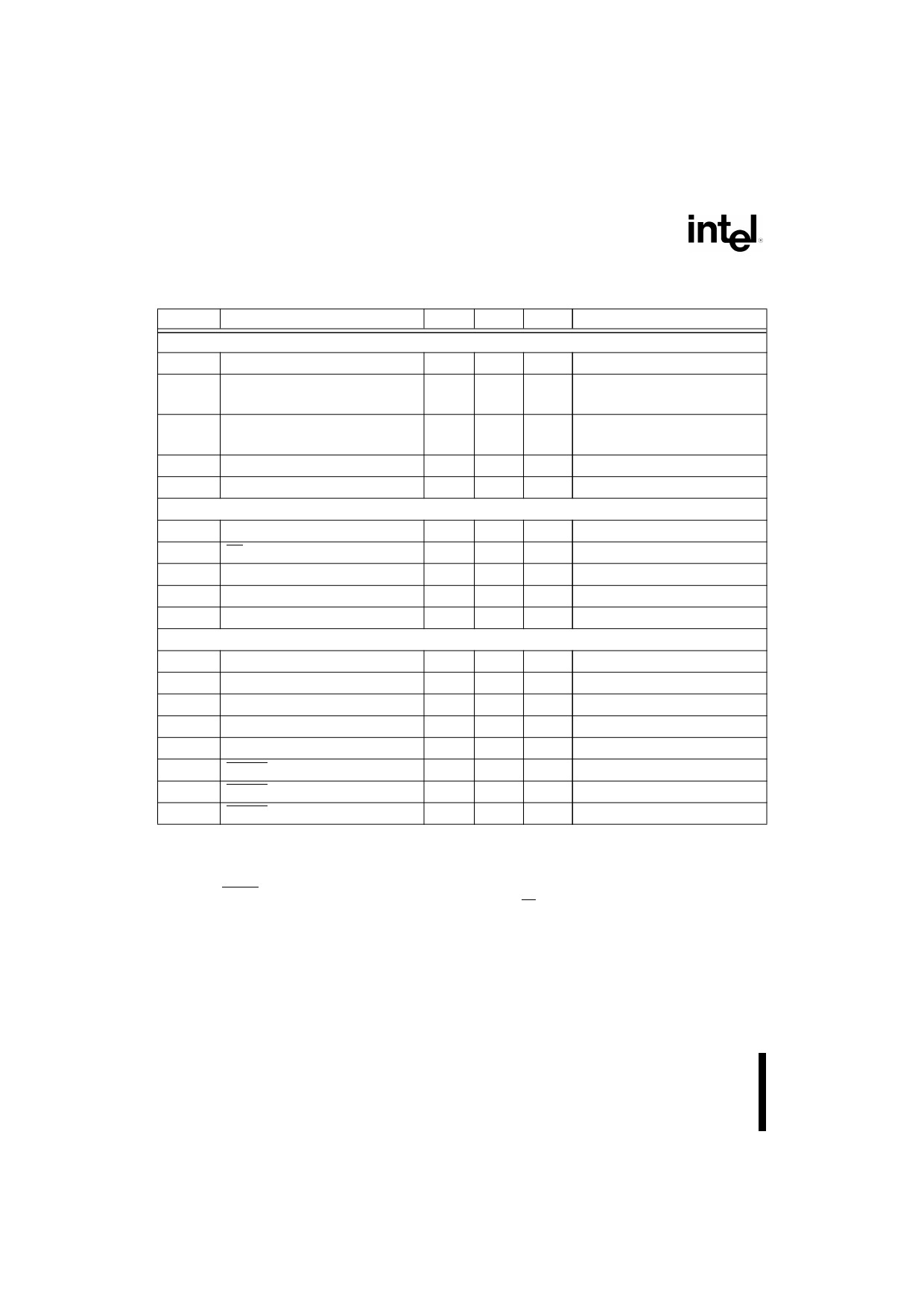

Table 6. 80960SA AC Characteristics (10 MHz)

Symbol

Parameter

Min Max Units

Notes

Input Clock

T1

Processor Clock Period (CLK2)

50

125

ns VIN = 1.5V

T2

Processor Clock Low Time (CLK2) 8

ns VT = 10% Point

= VCL + (VCH – VCL) x 0.1

T3

Processor Clock High Time

8

(CLK2)

ns VT = 90% Point

= VCL + (VCH – VCL) x 0.9

T4

Processor Clock Fall Time (CLK2)

10

ns VT = 90% to 10% Point (1)

T5

Processor Clock Rise Time (CLK2)

10

ns VT = 10% to 90% Point (1)

Synchronous Outputs

T6

Output Valid Delay

T6AS

AS Output Valid Delay

T7

ALE Width

T8

ALE Output Valid Delay

T9

Output Float Delay

Synchronous Inputs

2

31

2

25

T1 - 11

4

33

2

20

ns

ns

ns

ns

ns (2)

T10

Input Setup 1

10

ns

T11

Input Hold

2

ns

T12

Input Setup 2

13

ns

T13

Setup to ALE Inactive

10

ns

T14

Hold after ALE Inactive

8

ns

T15

RESET Hold

3

ns (3)

T16

RESET Setup

5

ns (3)

T17

RESET Width

2050

ns 41 CLK2 Periods Minimum

NOTES:

1. Processor clock (CLK2) rise time and fall time are not tested.

2. A float condition occurs when the maximum output current becomes less than ILO. Float delay is not tested, but should be

no longer than the valid delay.

3. Meeting RESET setup and hold times is an optional method of synchronizing your clocks. If you decide to use an asyn-

chronous reset, synchronizing the clock can be accomplished by using AS.

16