MAX791M(1995) 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

MAX791M Datasheet PDF : 20 Pages

| |||

Microprocessor Supervisory Circuit

+5V

R1

VCC

PFI

PFO

MAX791

R2

V-

+5V

PFO

0V

5

- 1.25

R1

=

1.25

- VTRIP

R2

NOTE: VTRIP IS NEGATIVE

GND

VTRIP

0V

V-

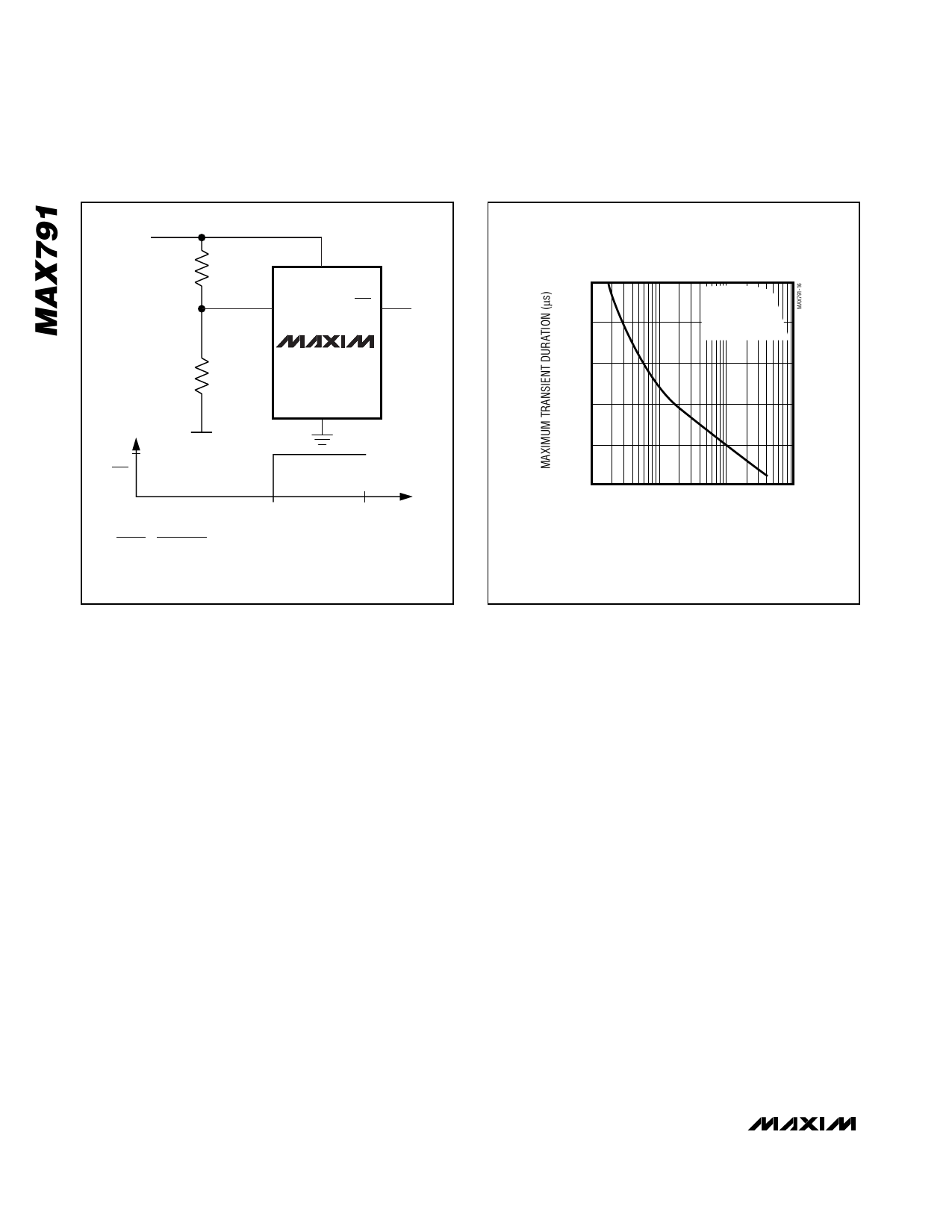

Figure 15. Monitoring a Negative Voltage

100

VCC = +5V

TA = +25°C

80

0.1µF CAPACITOR

FROM VOUT TO GND

60

40

20

0

10

100

1000

10,000

RESET COMPARATOR OVERDRIVE (mV)

(Reset Threshold Voltage - VCC)

Figure 16. Maximum Transient Duration without Causing a

Reset Pulse vs. Reset Comparator Overdrive

Monitoring a Negative Voltage

The power-fail comparator can be used to monitor a

negative supply voltage using Figure 15’s circuit. When

the negative supply is valid, PFO is low. When the neg-

ative supply voltage drops, PFO goes high. This cir-

cuit’s accuracy is affected by the PFI threshold toler-

ance, the VCC voltage, and resistors R1 and R2.

Backup-Battery Replacement

The backup battery may be disconnected while VCC is

above the reset threshold. No precautions are neces-

sary to avoid spurious reset pulses.

Negative-Going VCC Transients

While issuing resets to the µP during power-up, power-

down, and brownout conditions, these supervisors are

relatively immune to short-duration negative-going VCC

transients (glitches). It is usually undesirable to reset

the µP when VCC experiences only small glitches.

Figure 16 shows maximum transient duration vs. reset

comparator overdrive, for which reset pulses are not

generated. The graph was produced using negative-

going VCC pulses, starting at 5V and ending below the

reset threshold by the magnitude indicated (reset com-

parator overdrive). The graph shows the maximum

pulse width that a negative-going VCC transient may

typically have without causing a reset pulse to be

issued. As the amplitude of the transient increases (i.e.,

goes farther below the reset threshold), the maximum

allowable pulse width decreases. Typically, a VCC tran-

sient that goes 100mV below the reset threshold and

lasts for 40µs or less will not cause a reset pulse to be

issued.

A 100nF bypass capacitor mounted close to the VCC

pin provides additional transient immunity.

Connecting a Timing Capacitor to SWT

SWT is internally connected to a ±100nA current

source. When a capacitor is connected from SWT to

ground (to select an alternative watchdog timeout peri-

od), the current source charges and discharges the

timing capacitor to create the oscillator that controls the

watchdog timeout period. To prevent timing errors or

oscillator start-up problems, minimize external current

leakage sources at this pin, and locate the capacitor as

close to SWT as possible. The sum of PC board leak-

age + SWT capacitor leakage must be small compared

to ±100nA.

16 ______________________________________________________________________________________