ADC0808CCN жҹҘзңӢж•ёж“ҡиЎЁпјҲPDFпјү - Micro Linear Corporation

йӣ¶д»¶зј–еҸ·

дә§е“ҒжҸҸиҝ° (еҠҹиғҪ)

з”ҹдә§еҺӮ家

ADC0808CCN Datasheet PDF : 12 Pages

| |||

ML2258

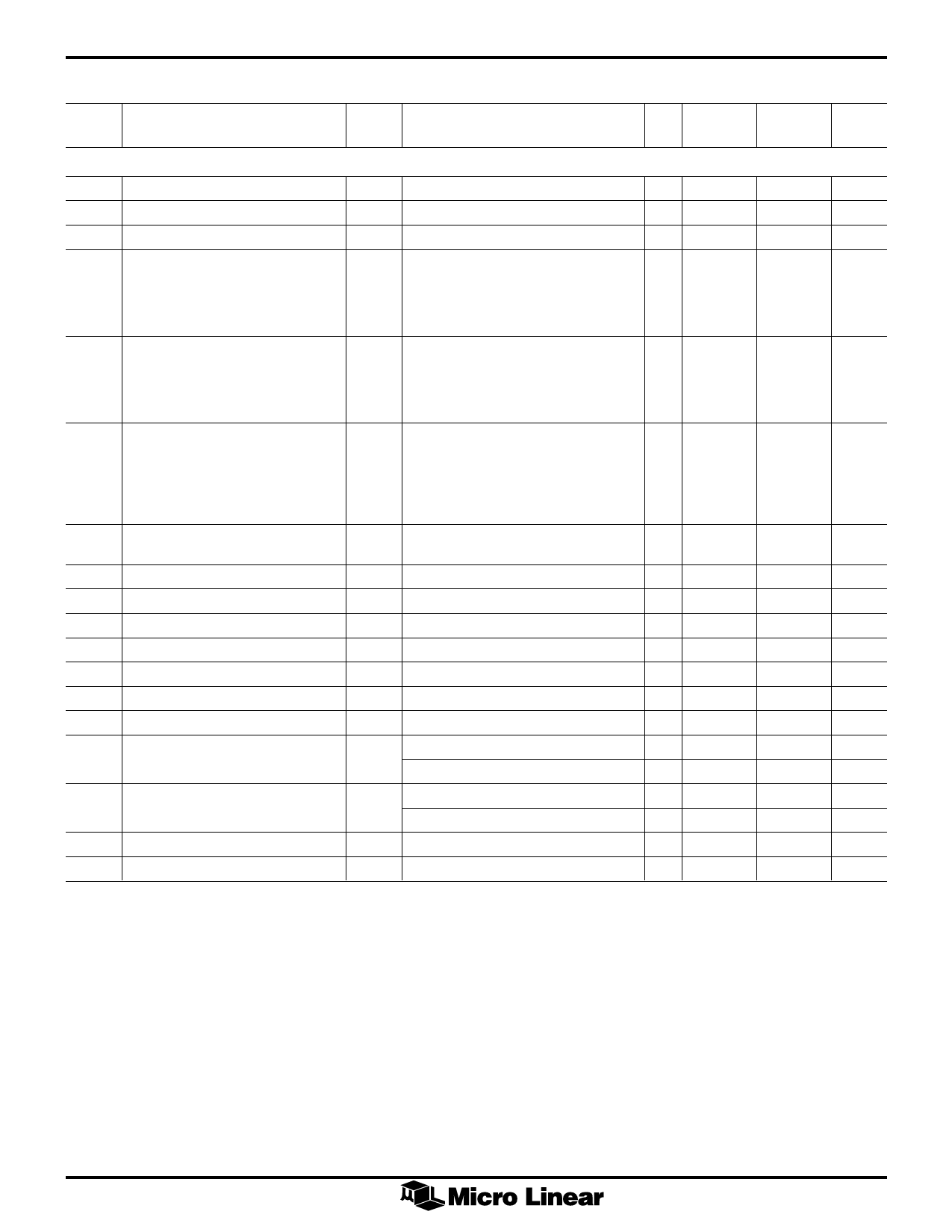

ELECTRICAL CHARACTERISTICS (Continued)

SYMBOL

PARAMETER

NOTES

CONDITIONS

TYP

MIN (NOTE 4)

MAX

UNITS

AC and Dynamic Performance Characteristics (Note 10)

tACQ

fCLK

tC

SNR

Sample and Hold Acquisition

Clock Frequency

Conversion Time

Signal to Noise Ratio

THD Total Harmonic Distortion

5

100

5

VIN = 51kHz, 5V sine.

fCLK = 10.24MHz

(fSAMPLING > 150kHz). Noise is sum

of all nonfundamental components

up to 1/2 of fSAMPLING

VIN = 51kHz, 5V sine.

fCLK = 10.24MHz

(fSAMPLING > 150kHz). THD is sum

of 2, 3, 4, 5 harmonics relative to

fundamental

IMD Intermodulation Distortion

FR

Frequency Response

VIN = fA + fB. fA = 49kHz, 2.5V sine.

fB = 47.8kHz, 2.5V sine,

fCLK = 10.24MHz

(fSAMPLING > 150kHz). IMD is (fA + fB),

(fA вҖ“ fB), (2fA + fB), (2fA вҖ“ fB), (fA + 2fB),

(fA вҖ“ 2fB) relative to fundamental

VIN = 0 to 50kHz. 5V sine relative

to 1kHz

tDC

Clock Duty Cycle

6, 11

40

tEOC

End of Conversion Delay

5

tWS

Start Pulse Width

5

50

tSS

Start Pulse Setup Time

6, 12 Synchronous only

40

tWALE Address Latch Enable Pulse Width 5

50

tS

Address Setup

5

0

tH

Address Hold

5

50

tH1, H0 Output Enable for DB0вҖ“DB7

6 Figure 1, CL = 50pF

6 Figure 1, CL = 10pF

t1H, 0H Output Disable for DB0вҖ“DB7

6 Figure 1, CL = 50pF

6 Figure 1, CL = 10pF

CIN

Capacitance of Logic Input

COUT Capacitance of Logic Outputs

4

1/fCLK

10240 kHz

67 67 + 250ns 1/fCLK

47

dB

вҖ“60

dB

вҖ“60

dB

0.1

dB

60

%

8

8 + 250ns 1/fCLK

ns

ns

ns

ns

ns

100

ns

50

ns

200

ns

100

ns

5

pF

10

pF

Note 1: Absolute maximum ratings are limits beyond which the life of the integrated circuit may be impaired. All voltages unless otherwise specified are measured with

respect to ground.

Note 2: When the input voltage (VIN) at any pin exceeds the power supply rails (VIN < VвҖ“ or VIN > V+) the absolute value of current at that pin should be limited to 25mA or less.

Note 3: вҖ“40В°C to +85В°C operating temperature range devices are 100% tested with temperature limits guaranteed by 100% testing, sampling, or by correlation with worst-

case test conditions.

Note 4: Typicals are parametric norm at 25В°C.

Note 5: Parameter guaranteed and 100% production tested.

Note 6: Parameter guaranteed. Parameters not 100% tested are not in outgoing quality level calculation.

Note 7: Total unadjusted error includes offset, full scale, linearity, multiplexer and sample and hold errors.

Note 8: For вҖ“VREF вҖў VIN (+) the digital output code will be 0000 0000. Two on-chip diodes are tied to each analog input which will forward conduct for analog input voltages

one diode drop below ground or one diode drop greater than the VCC supply. Be careful, during testing at low VCC levels (4.5V), as high level analog inputs (5V) can

cause this input diode to conduct вҖ” especially at elevated temperatures, and cause errors for analog inputs near full scale. The spec allow 100mV forward bias of either

diode. This means that as long as the analog VIN or VREF does not exceed the supply voltage by more than 100mV, the output code will be correct. To achieve an

absolute 0VDC to 5VDC input voltage range will therefore require a minimum supply voltage of 4.900VDC over temperature variations, initial tolerance and loading.

Note 9: Leakage current is measured with the clock not switching.

Note 10: CL = 50pF, timing measured at 50% point.

Note 11: A 40% to 60% clock duty cycle range insures proper operation at all clock frequencies. In the case that an available clock has a duty cycle outside of these limits,

the minimum time the clock is high or the minimum time the clock is low must be at least 40ns. The maximum time the clock can be high or low is 60Вөs.

Note 12: The conversion start setup time requirement only needs to be satisfied if a conversion must be synchronized to a given clock rising edge. If the setup time is not met,

start conversion will have an uncertainty of one clock pulse.

4