PCF8575CTS/F1 查看數據表(PDF) - Philips Electronics

零件编号

产品描述 (功能)

生产厂家

PCF8575CTS/F1 Datasheet PDF : 24 Pages

| |||

Philips Semiconductors

Remote 16-bit I/O expander for I2C-bus

Product specification

PCF8575C

6.3 Reading from a port (input mode)

All ports programmed as input should be set to logic 1.

To read, the master (microcontroller) first addresses the

slave device after it receives the interrupt. By setting the

last bit of the byte containing the slave address to logic 1

the read mode is entered. The data bytes that follow on the

SDA are the values on the ports.

If the data on the input port changes faster than the master

can read, this data may be lost.

6.4 Writing to the port (output mode)

To write, the master (microcontroller) first addresses the

slave device. By setting the last bit of the byte containing

the slave address to logic 0 the write mode is entered. The

PCF8575C acknowledges and the master sends the first

data byte for P07 to P00. After the first data byte is

acknowledged by the PCF8575C, the second data byte

P17 to P10 is sent by the master. Once again the

PCF8575C acknowledges the receipt of the data after

which this 16-bit data is presented on the port lines.

The number of data bytes that can be sent successively is

not limited. After every two bytes the previous data is

overwritten.

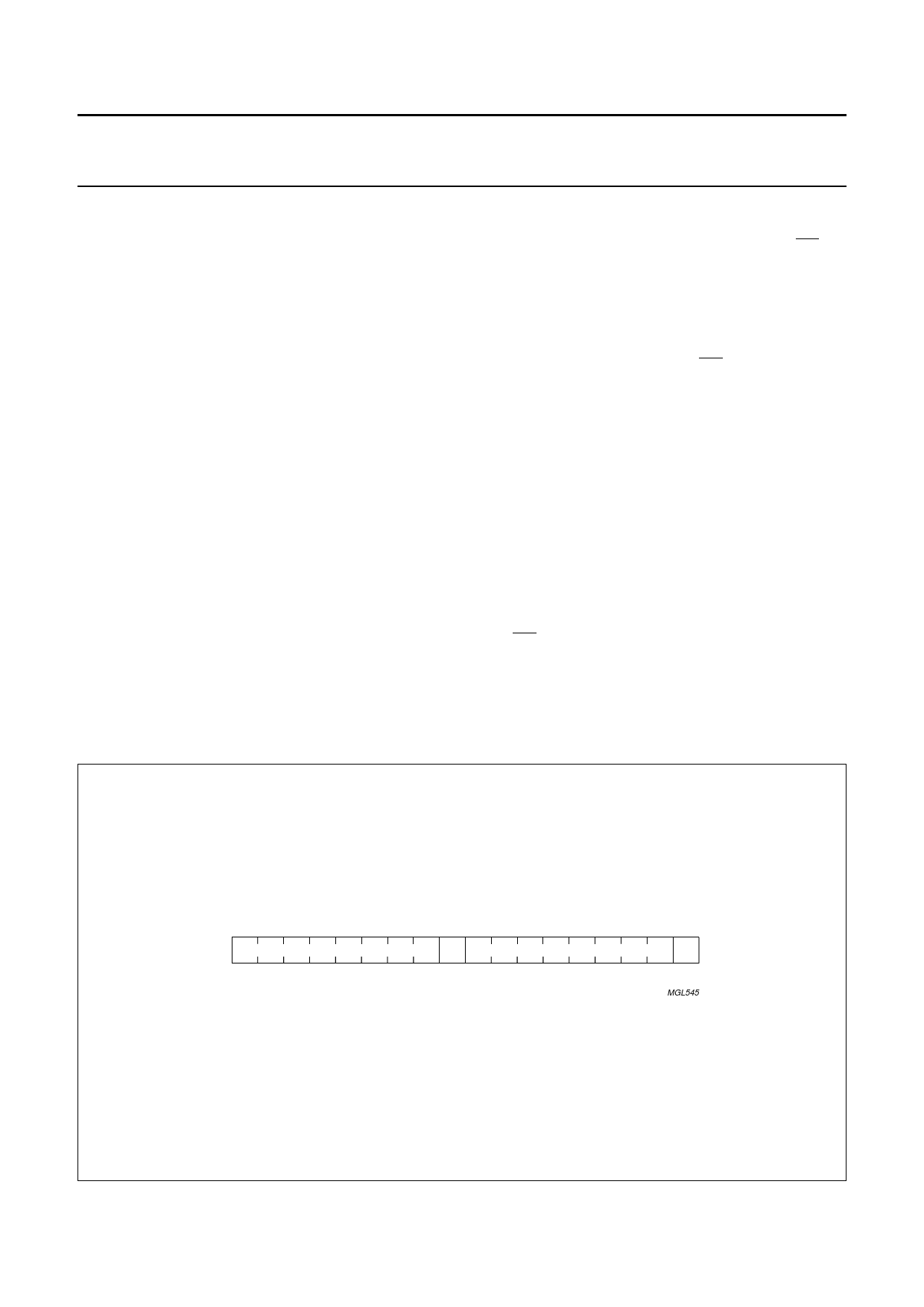

The first data byte in every pair refers to Port 0

(P07 to P00), whereas the second data byte in every pair

refers to Port 1 (P17 to P10), see Fig.7.

6.5 Interrupt

The PCF8575C provides an open-drain interrupt (INT)

which can be fed to a corresponding input of the

microcontroller (see Figs 5, 6 and 8). This gives these

chips a kind of a master function which can initiate an

action elsewhere in the system.

An interrupt is generated by any rising or falling edge of the

port inputs. After time tiv the signal INT is valid.

The interrupt disappears when data on the port is changed

to the original setting or data is read from or written to the

device which has generated the interrupt.

In the write mode the interrupt may become deactivated

(HIGH) on the rising edge of the write to port pulse. On the

falling edge of the write to port pulse the interrupt is

definitely deactivated (HIGH).

The interrupt is reset in the read mode on the rising edge

of the read from port pulse.

During the resetting of the interrupt itself any changes on

the I/Os may not generate an interrupt. After the interrupt

is reset any change in I/Os will be detected and transmitted

as an INT.

handbook, full pagewidth

First Byte

Second Byte

07 06 05 04 03 02 01 00 A 17 16 15 14 13 12 11 10 A

P07 P06 P05 P04 P03 P02 P01 P00

P17 P16 P15 P14 P13 P12 P11 P10

MGL545

1999 Aug 05

Fig.7 Correlation between bits and ports.

9