AM85C30-8PC 查看數據表(PDF) - Advanced Micro Devices

零件编号

产品描述 (功能)

生产厂家

AM85C30-8PC Datasheet PDF : 68 Pages

| |||

AMD

Data Path

The transmit and receive data path illustrated in Figure 2

is identical for both channels. The receiver has three

8-bit buffer registers in a FIFO arrangement, in addition

to the 8-bit receive shift register. This scheme creates

additional time for the CPU to service an interrupt at the

beginning of a block of high-speed data. Incoming data

are routed through one of several paths (data or CRC)

depending on the selected mode (the character length

in asynchronous modes also determines the data path).

The transmitter has an 8-bit transmit data buffer register

loaded from the internal data bus and a 20-bit transmit

shift register that can be loaded either from the sync-

character registers or from the transmit data register.

Depending on the operational mode, outgoing data are

routed through one of four main paths before they are

transmitted from the Transmit Data output (TxD).

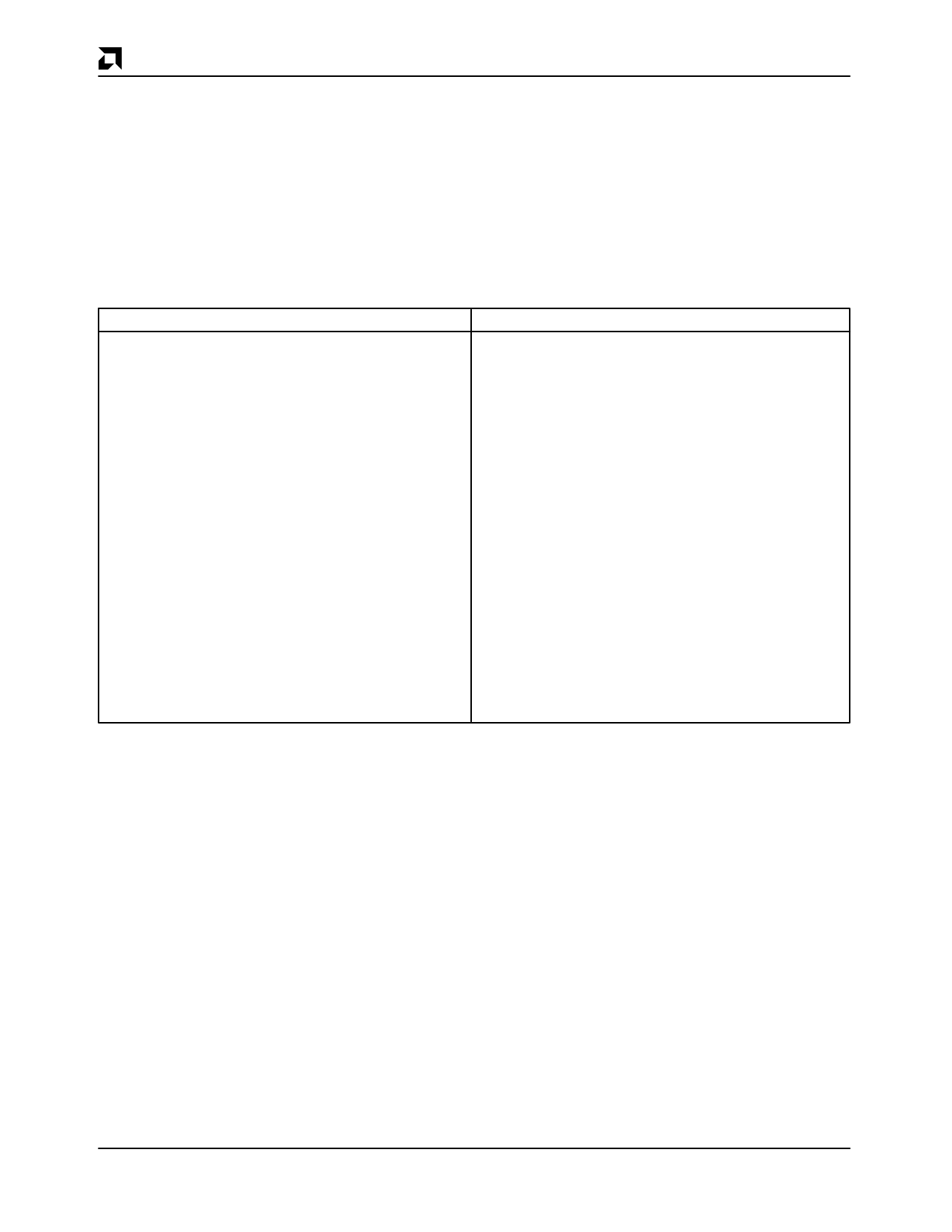

Table 1. Read and Write Register Functions

Read Register Functions

Write Register Functions

RR0 Transmit/Receive buffer status and External

status

RR1 Special Receive Condition status

(also 10 × 19 bit FIFO Frame Reception Status if

WR15 bit D2 is set)

RR2 Modified interrupt vector

(Channel B only)

Unmodified interrupt vector

(Channel A only)

RR3 Interrupt Pending bits

(Channel A only)

RR6 LSB Byte Count (14-bit counter)

(if WR15 bit D2 set)

RR7 MSB Byte Count (14-bit counter)

and 10 × 19 bit FIFO Status (if WR15 bit D2 is set)

RR8 Receive buffer

RR10 Miscellaneous XMTR, RCVR status

RR12 Lower byte of baud rate generator time constant

RR13 Upper byte of baud rate generator time constant

RR15 External/Status interrupt information

Write Register Functions

WR0

WR1

WR2

WR3

WR4

WR5

WR6

WR7

WR7′

WR8

WR9

WR10

WR11

WR12

WR13

WR14

WR15

Command Register, Register Pointers CRC

initialize, initialization commands for the various

modes, shift right/shift left command

Interrupt conditions and data transfer mode

definition

Interrupt vector (accessed through either channel)

Receive parameters and control

Transmit/Receive miscellaneous parameters and

modes

Transmit parameters and controls

Sync character or SDLC address field

Sync character or SDLC flag

SDLC/HDLC enhancements (if bit D0 of WR15 is

set)

Transmit buffer

Master interrupt control and reset (accessed

through either channel)

Miscellaneous transmitter/receiver control bits,

data encoding

Clock mode control, Rx and Tx clock source

Lower byte of baud rate generator time constant

Upper byte of baud rate generator time constant

Miscellaneous control bits, DPLL control

External/Status interrupt control

10

Am85C30