EDS1232AABB 查看數據表(PDF) - Elpida Memory, Inc

零件编号

产品描述 (功能)

生产厂家

EDS1232AABB Datasheet PDF : 55 Pages

| |||

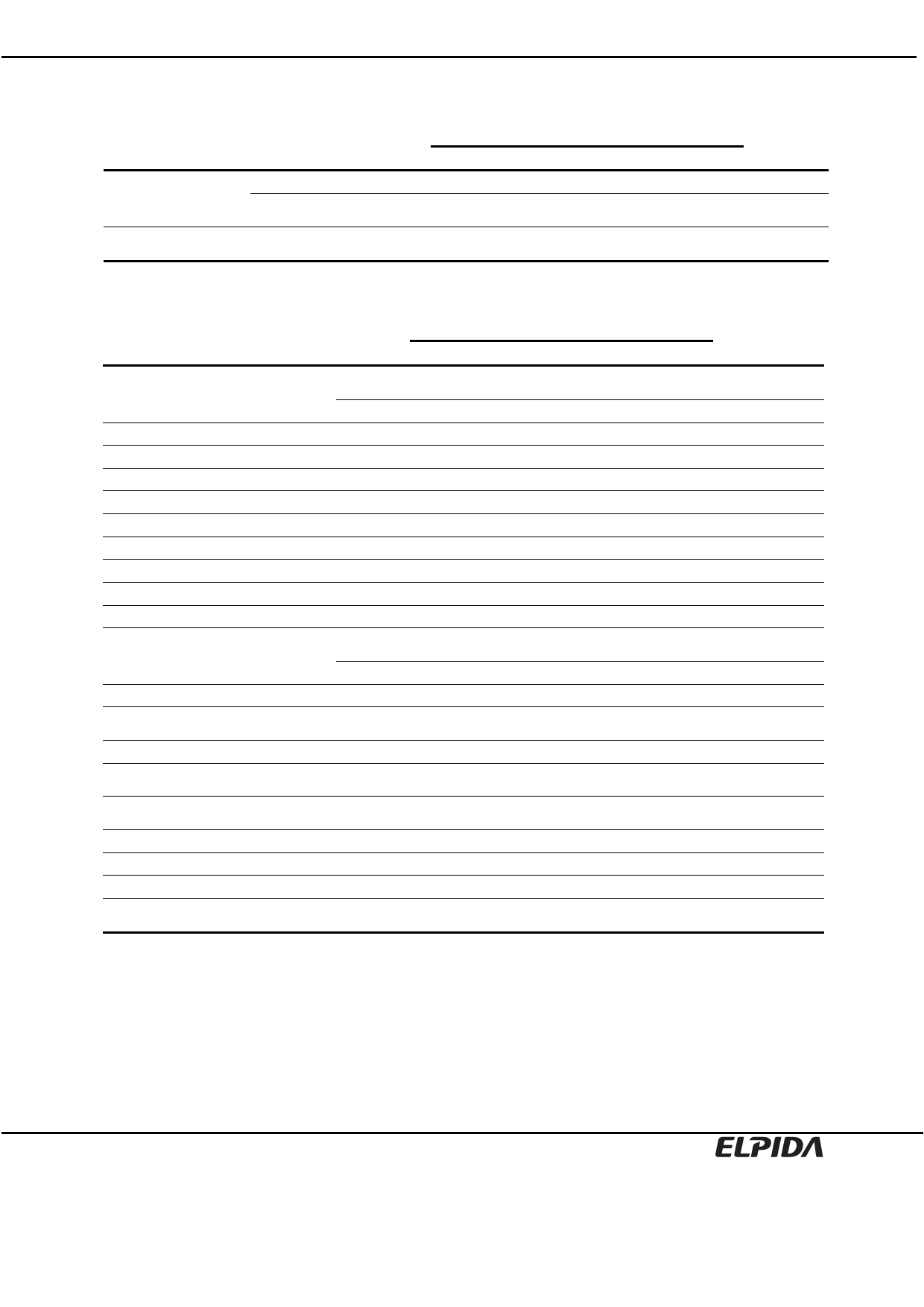

EDS1232AABB, EDS1232AATA

Pin Capacitance (TA = 25°C, f = 1MHz)

Parameter

Input capacitance

Data input/output

capacitance

90-ball FBGA

Symbol Pins

min. Typ

CI1 Address

1.5

—

CI2

CLK, CKE, /CS, /RAS,

/CAS, /WE, DQM

1.5

—

CI/O DQ

3.0

—

max.

3.0

3.0

86-pin TSOP (II)

min. Typ max.

2.5

—

4.0

2.5

—

4.0

Unit Notes

pF

pF

5.5

4.0

—

6.5

pF

AC Characteristics (TA = 0 to +70°C, VDD, VDDQ = 3.3V±0.3V, VSS, VSSQ = 0V)

-60

-75

Parameter

Symbol

min.

max.

min.

max.

Unit

Notes

System clock cycle time

(CL = 2)

(CL = 3)

tCK

7.5

—

10

—

ns

tCK

6

—

7.5

—

ns

CLK high pulse width

tCH

2.5

—

2.5

—

ns

CLK low pulse width

tCL

2.5

—

2.5

—

ns

Access time from CLK

tAC

—

5.4

—

5.4

ns

Data-out hold time

tOH

2

—

2

—

ns

CLK to Data-out low impedance

tLZ

0

—

0

—

ns

CLK to Data-out high impedance

tHZ

2

5.4

2

5.4

ns

Input setup time

tSI

1.5

—

1.5

—

ns

Input hold time

tHI

0.8

—

0.8

—

ns

CKE setup time (Power down exit)

tCKSP

1.5

—

1.5

—

ns

ACT to REF/ACT command period

(operation)

tRC

60

67.5

ns

(refresh)

tRC

60

67.5

ns

Active to Precharge command period tRAS

42

120000

45

120000

ns

Active command to column command

(same bank)

tRCD

15

20

ns

Precharge to active command period tRP

15

20

ns

Write recovery or data-in to precharge

lead time

tDPL

12

15

ns

Last data into active latency

tDAL

2CLK +

15ns

2CLK +

20ns

Active (a) to Active (b) command period tRRD

12

15

ns

Mode register set cycle time

tRSC

2

2

CLK

Transition time (rise and fall)

Refresh period

(4096 refresh cycles)

tT

0.5

30

0.5

30

ns

tREF

—

64

—

64

ms

Preliminary Data Sheet E0205E50 (Ver. 5.0)

7