NT128S64VH4A0GM0-7K 查看數據表(PDF) - Nanya Technology

零件编号

产品描述 (功能)

生产厂家

NT128S64VH4A0GM0-7K

NT128S64VH4A0GM0-7K Datasheet PDF : 12 Pages

| |||

NT128S64VH4A0GM

128MB : 16M x 64

SDRAM SODIMM

16Mx64 bit One Bank Small Outline SDRAM Module

based on 16Mx16, 4Banks, 8K Refresh, 3.3V Synchronous DRAMs with SPD

Features

l 144 Pin JEDEC Standard, 8 Byte Small Outline Dual-In-line

Memory Module

l 16Mx64 Synchronous DRAM SO DIMM

l Inputs and outputs are LVTTL (3.3V) compatible

l 10 Ohm Resistors on DQs

l Single 3.3V ± 0.3V Power Supply

l Single Pulsed RAS interface

l SDRAMs have four internal banks

l Fully Synchronous to positive Clock Edge

l Data Mask for Byte Read/Write control

l Auto Refresh (CBR) and Self Refresh

l Automatic and controlled Precharge Commands

l Programmable Operation:

- CAS Latency: 2, 3

- Burst Type: Sequential or Interleave

- Burst Length: 1, 2, 4, 8,

- Operation: Burst Read and Write or Multiple Burst Read with

Single Write

l Suspend Mode and Power Down Mode

l 13/9/2 Addressing (Row/Column/Bank)

l 8192 refresh cycles distributed across 64ms

l Serial Presence Detect

l Gold contacts

Description

NT128S64VH4A0GM is a 144-pin Synchronous DRAM Small Outline Dual In-line Memory Module (SO DIMM) that is organized as a 16Mx64

high-speed memory array. The SO DIMM uses four 16Mx16 SDRAMs in 400mil TSOP II packages and achieves high-speed data transfer rates

of up to 133 MHz by employing a prefetch / pipeline hybrid architecture that supports the JEDEC 1N rule while allowing very low burst power.

All control, address, and data input/output circuits are synchronized with the positive edge of the externally supplied clock inputs. All inputs are

sampled at the positive edge of the externally supplied clock (CK0). Internal operating modes are defined by combinations of the

RAS , CAS , WE , S0 , DQMB, and CKE0 signals. A command decoder initiates the necessary timings for each operation. A 15 bit

address bus accepts address information in a row/column multiplexing arrangement.

Prior to any access operation, the CAS latency, burst type, burst length, and burst operation type must be programmed into the SO DIMM by

address inputs A0-A9 during the mode register set cycle. The SO DIMM uses serial presence detects implemented via a serial EEPROM using

the two pin IIC protocol. The first 128 bytes of serial PD data are used by the DIMM manufacturer. The last 128 bytes are available to the

customer.

All Nanya 144-pin SO DIMMs provide a high performance, flexible 8-byte interface in a 2.66" long space-saving footprint.

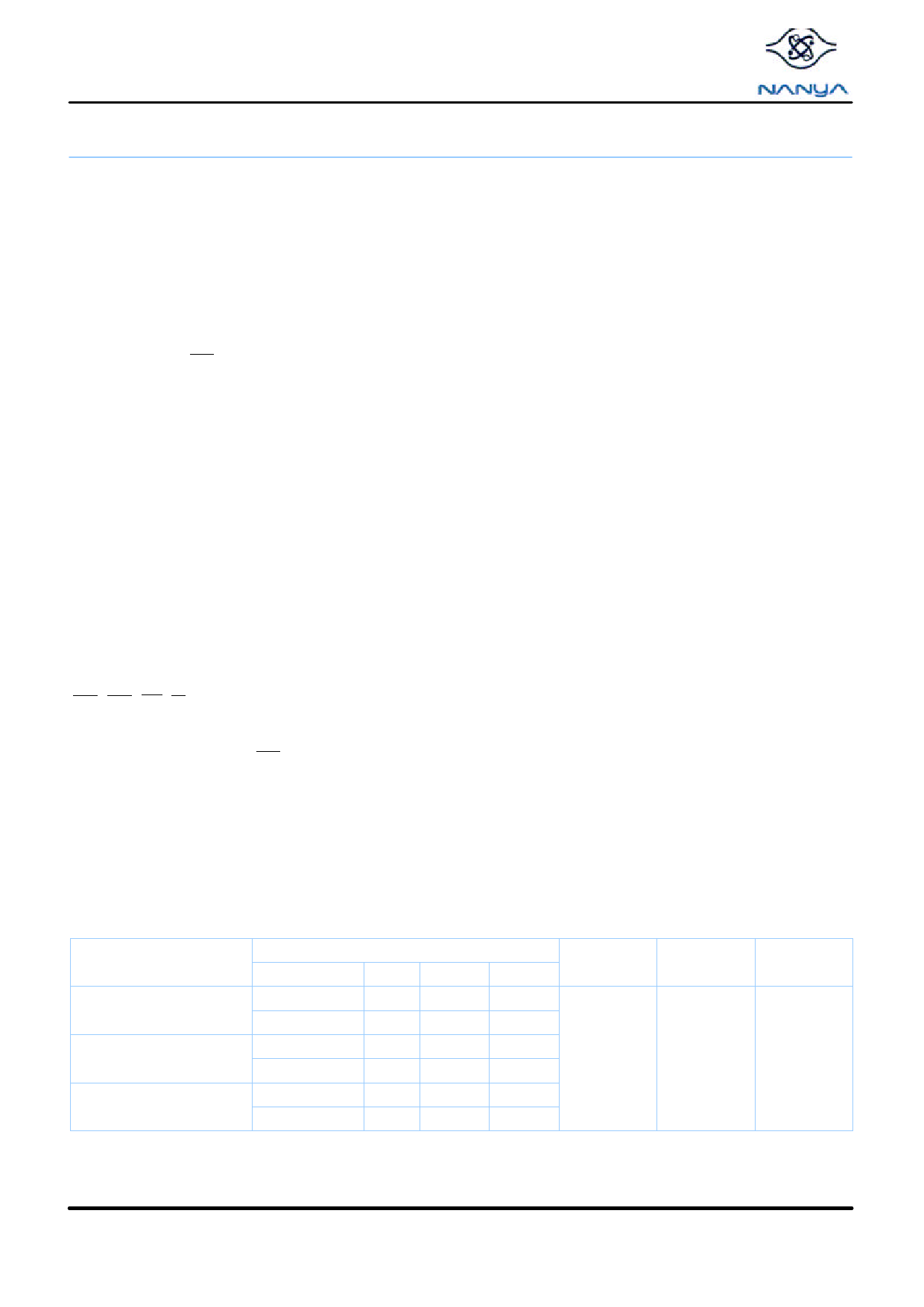

Ordering Information

Part Number

NT128S64VH4A0GM-7K

NT128S64VH4A0GM-75B

NT128S64VH4A0GM-8B

* CL = CAS Latency

MHz.

143MHz

133MHz

133MHz

100MHz

125MHz

100MHz

Speed

CL

t RCD

3

3

2

2

3

3

2

2

3

3

2

2

Organization

t RP

3

2

3

16Mx64

2

3

2

Leads

Gold

Power

3.3V

PRELIMINARY 08 /2001

1

© NANYA TECHNOLOGY CORP.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.