NT128D64S88A2GM 查看數據表(PDF) - Nanya Technology

零件编号

产品描述 (功能)

生产厂家

NT128D64S88A2GM

NT128D64S88A2GM Datasheet PDF : 14 Pages

| |||

NT128D64S88A2GM

128MB : 16M x 64

PC2100 / PC1600 Unbuffered DDR SO-DIMM

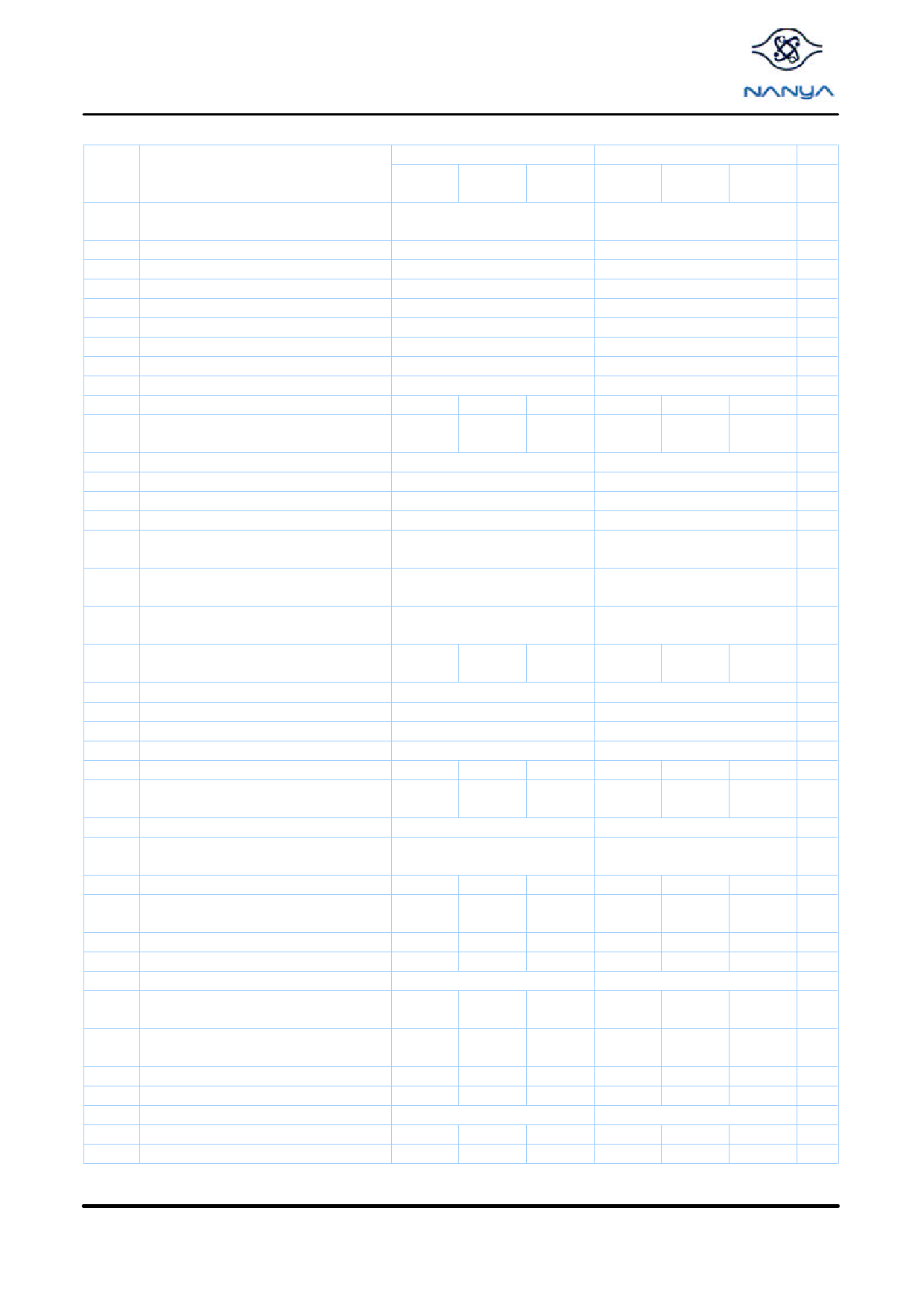

Serial Presence Detect -- Part 1 of 2

Byte

Description

0

1

2

3

4

5

6.

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36-61

62

63

Number of Serial PD Bytes Written during

Production

Total Number of Bytes in Serial PD device

Fundamental Memory Type

Number of Row Addresses on Assembly

Number of Column Addresses on Assembly

Number of DIMM Bank

Data Width of Assembly

Data Width of Assembly (cont’)

Voltage Interface Level of this Assembly

DDR SDRAM Device Cycle Time at CL=2.5

DDR SDRAM Device Access Time from

Clock at CL=2.5

DIMM Configuration Type

Refresh Rate/Type

Primary DDR SDRAM Width

Error Checking DDR SDRAM Device Width

DDR SDRAM Device Attr: Min CLk Delay,

Random Col Access

DDR SDRAM Device Attributes:

Burst Length Supported

DDR SDRAM Device Attributes: Number of

Device Banks

DDR SDRAM Device Attributes: CAS

Latencies Supported

DDR SDRAM Device Attributes: CS Latency

DDR SDRAM Device Attributes: WE Latency

DDR SDRAM Device Attributes:

DDR SDRAM Device Attributes: General

Minimum Clock Cycle at CL=2

Maximum Data Access Time from Clock at

CL=2

Minimum Clock Cycle Time at CL=1

Maximum Data Access Time from Clock at

CL=1

Minimum Row Precharge Time(tRP)

Minimum Row Active to Row Active delay

(tRRD)

Minimum RAS to CAS delay (tRCD)

Minimum RAS Pulse Width (tRAS)

Module Bank Density

Address and Command Setup Time Before

Clock

Address and Command Hold Time After

Clock

Data Input Setup Time Before Clock

Data Input Hold Time After Clock

Reserved

SPD Revision

Checksum Data

SPD Entry Value

DDR266A DDR266B DDR200

-7K

-75B

-8B

128

256

DDR SDRAM

12

10

1

X64

X64

SSTL 2.5V

7ns

7.5ns

8ns

0.75ns 0.75ns

0.8ns

Non-Parity

SR/1x(15.625us)

X8

N/A

1 Clock

2,4,8

4

2/2.5

2/2.5

2/2.5

0

1

Differential Clock

+/-0.2V Voltage Tolerance

7.5ns

10ns

10ns

0.75ns 0.75ns

0.8ns

N/A

N/A

20ns

20ns

20ns

15ns

15ns

15ns

20ns

45ns

20ns

45ns

128MB

20ns

50ns

0.9ns

0.9ns

1.1ns

0.9ns

0.5ns

0.5ns

Initial

0.9ns

0.5ns

0.5ns

Undefined

Initial

1.1ns

0.6ns

0.6ns

Initial

Serial PD Data Entry (Hexadecimal)

DDR266A DDR266B DDR200

-7K

-75

-8B

Note

80

08

07

0C

0A

01

40

00

04

70

75

80

75

75

80

00

80

08

00

01

0E

04

0C

0C

0C

01

02

20

00

75

A0

A0

75

75

80

00

00

50

50

50

3C

3C

3C

50

50

50

2D

2D

32

20

90

90

B0

90

90

B0

50

50

60

50

50

60

00

00

00

00

6C

9C

22

Preliminary 01/2002

5

© NANYA TECHNOLOGY CORP.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.