TQ8105P 查看數據表(PDF) - TriQuint Semiconductor

零件编号

产品描述 (功能)

生产厂家

TQ8105P Datasheet PDF : 19 Pages

| |||

TQ8105/TQ8106

PRELIMINARY DATA SHEET

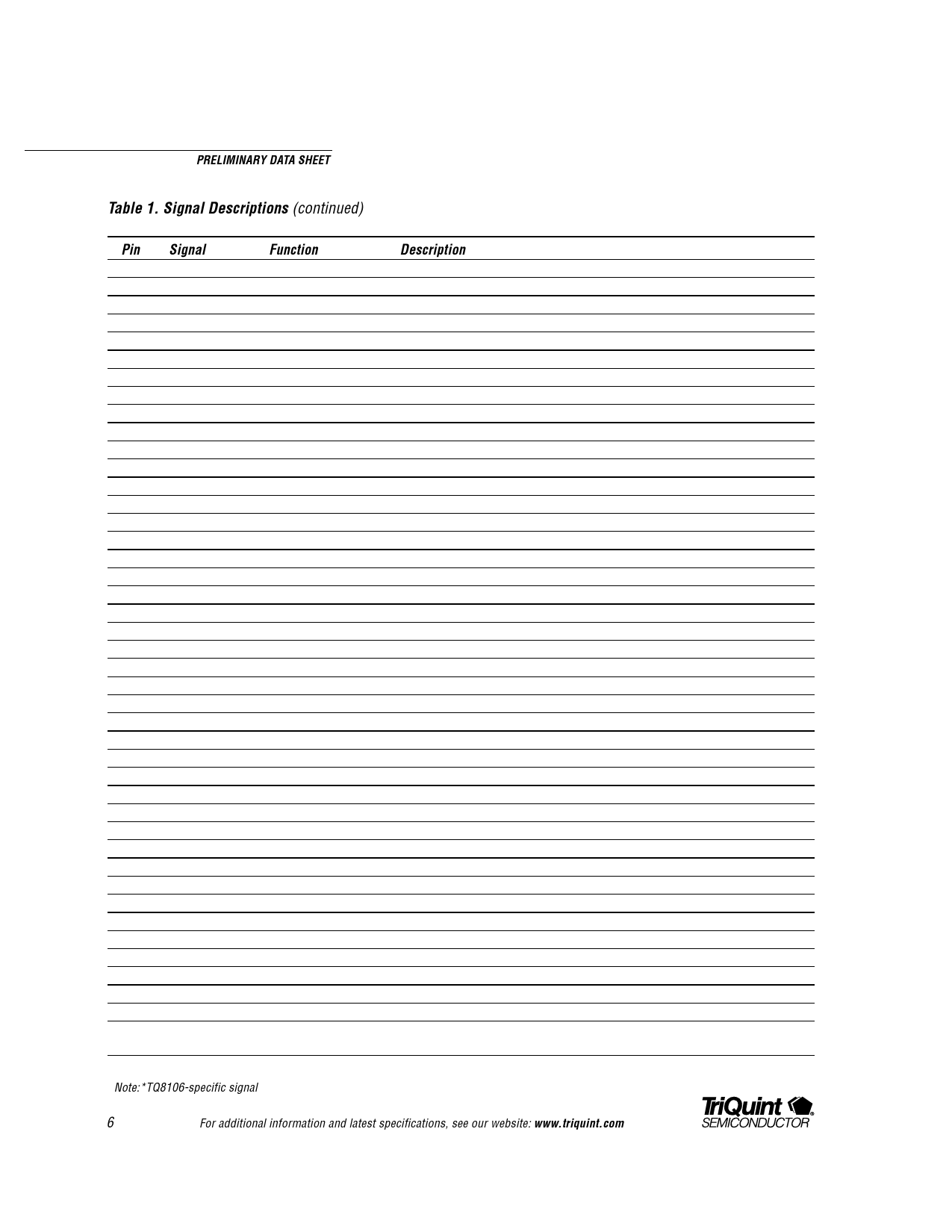

Table 1. Signal Descriptions (continued)

Pin Signal

Function

Description

58 CLRLOS

TTL Input

Active-high Clear LOS output

59 RLOCK

Tristate TTL Output Receive Clock meets lock criteria when high

60 LBM1

TTL Input

Loopback Mode Control (see Table 3)

61 GND

GND

Core Ground

62 LBM0

TTL Input

Loopback Mode Control (see Table 3)

63 VDD

+5V

Core Positive Supply

64 NOE

TTL Input

TTL tristate control (active low to enable)

65 GND

GND

Core Ground

66 NRESET

TTL Input

Global Reset (active low)

67 OC3

TTL Input

OC3/OC12 Mode Select

68 MMS

TTL Input

Master/Slave Mode Control

69 CKSRC2

TTL Input

Clock Source Select (see Table 3)

70 CKSRC1

TTL Input

Clock Source Select (see Table 3)

71 CKSRC0

TTL Input

Clock Source Select (see Table 3)

72 PH1

TTL Input

TxBC Phase Select (see Table 3)

73 PH0

TTL Input

TxBC Phase Select (see Table 3)

74 VDD

+5V

Core Positive Supply

75 SVDD

+5V

Output Driver Internal Positive Supply

76 GND

GND

Core Ground

77 MXD0

TTL Input

Multiplexer Data Bit 0 (LSB)

78 MXD1

TTL Input

Multiplexer Data Bit 1

79 MXD2

TTL Input

Multiplexer Data Bit 2

80 MXD3

TTL Input

Multiplexer Data Bit 3

81 MXD4

TTL Input

Multiplexer Data Bit 4

82 MXD5

TTL Input

Multiplexer Data Bit 5

83 MXD6

TTL Input

Multiplexer Data Bit 6

84 MXD7

TTL Input

Multiplexer Data Bit 7 (MSB)

85 VCC

+5V/+3.3V

TTL Driver Positive Supply

86 TxBC

Tristate TTL Out

Transmit Byte Clock

87 DGND

GND

TTL Driver Ground

88 SONETCK

Tristate TTL Out

51.84 MHz Clock Output

89 VCC

+5V/+3.3V

TTL Driver Positive Supply

90 SDHCK

Tristate TTL Out

38.88 MHz Clock Output

91 DGND

GND

TTL Driver Ground

92 LOR

Tristate TTL Out

Indicates Reference Clock is Absent

93 AGND

Analog Ground

VCO Analog Ground

94 FP2

Analog Output

Transmit PLL Loop Filter, Charge Pump Out

95 FP1

Analog Input

Transmit PLL Loop Filter, VCO Tune

96 AVDD

Analog +5V

VCO & Filter Analog VDD Supply

97 VDD

+5V

Core Positive Supply

98 REFCKT

TTL Input

Tx Reference Clock or Bypass Clock

99 GND

GND

Core Ground

100 NC/NCDREN* TTL Input

Internal Pull-up, Low = CDR receiver clock; Float = Pin 17/18 Rx Clk

(ignored by TQ8105)

Note:*TQ8106-specific signal

6

For additional information and latest specifications, see our website: www.triquint.com