STPCD0175BTC3 查看數據表(PDF) - STMicroelectronics

零件编号

产品描述 (功能)

生产厂家

STPCD0175BTC3 Datasheet PDF : 48 Pages

| |||

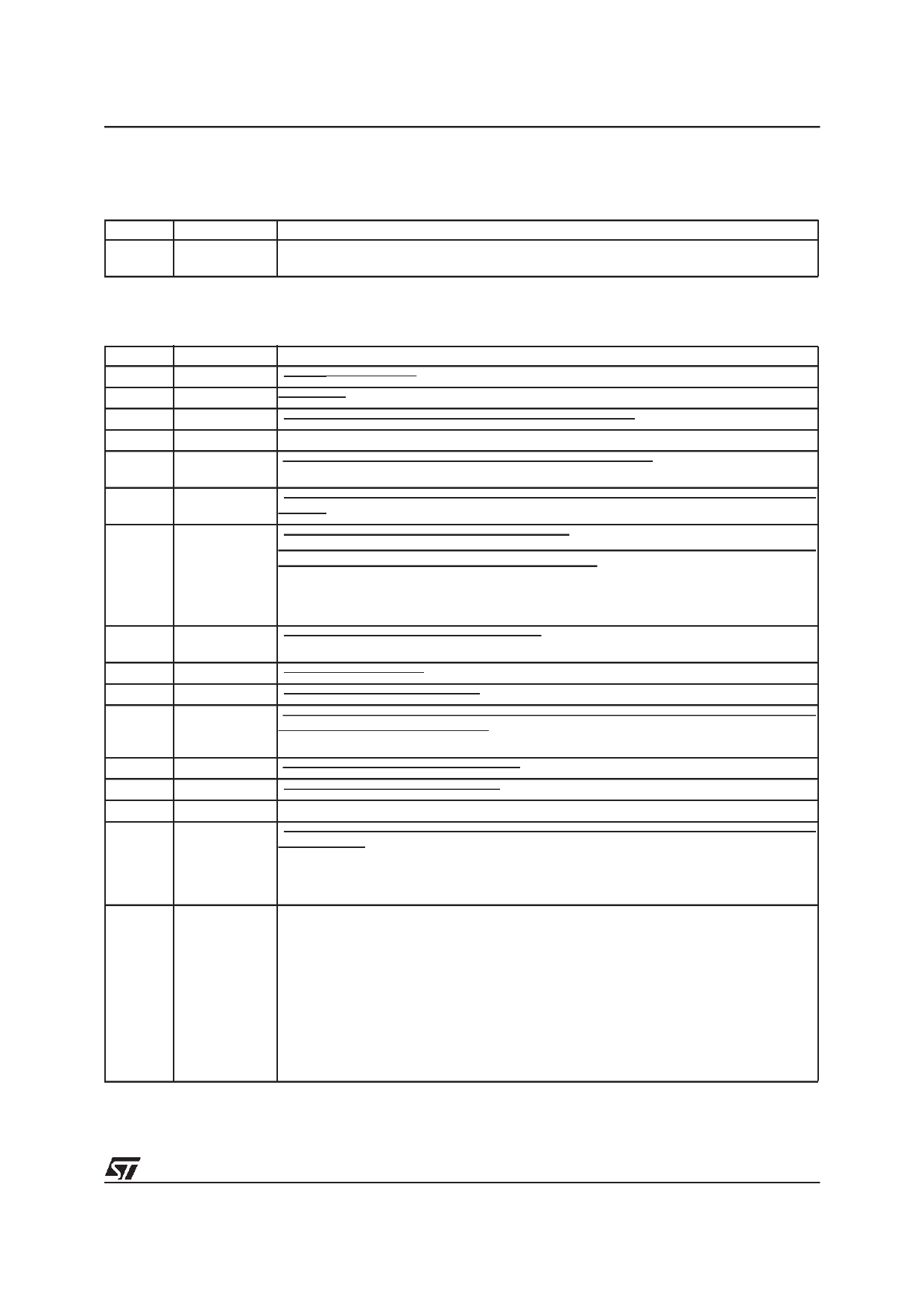

UPDATE HISTORY FOR OVERVIEW

UPDATE HISTORY FOR OVERVIEW

The following changes have been made to the Board Layout Chapter on 02/02/2000.

Section

Change

Added

Text

To check if your memory device is supported by the STPC, please refer to

Table 7-69 Host Address to MA Bus Mappingin the Programming Manual.

The following changes have been made to the Board Layout Chapter from Revision 1.0 to Release 1.2.

Section

N/A

N/A

N/A

N/A

N/A

Change

Replaced

Replaced

Removed

Removed

Replaced

N/A

Replaced

N/A

Replaced

N/A

Replaced

N/A

Removed

N/A

Replaced

N/A

Replaced

N/A

Replaced

N/A

Removed

N/A

Added

N/A

Replaced

N/A

Removed

Text

“fully PC compatible” With “with DOS, Windows and UNIX compatibility”

“133 MHz” With 75 MHz”

“Drivers for Windows and other operating systems.”

“Requires external frequency synthesizer and reference sources.”

“Chroma and colour keying for integrated video overlay.” With “Chroma and colour

keying allowing video overlay.

“Accepts video inputs in CCIR 601/656 or ITU-R 601/656, and decodes the

stream.” With “Decodes video inputs in ITU-R 601/656 compatible formats.

“Fully compliant with PCI 2.1 specification.

Integrated PCI arbitration interface. Up to 3 masters can connect directly.

External PAL allows for greater than 3 masters.”

With

“Integrated PCI arbitration interface able to directly manage up to 3 PCI

masters at a time.”

“0.33X and 0.5X CPU clock PCI clock.” With “The PCI clock runs at a third or

half CPU clock speed.”

“Supports flash ROM.”

“Supports ISA hidden refresh.” With “Supports flash ROM.”

“Buffered DMA & ISA master cycles to reduce bandwidth utilization of the PCI

and Host bus. NSP compliant.” With “Buffered DMA & ISA master cycles to

reduce bandwidth utilization of the PCI and Host bus. “

“Supports PIO and Bus Master IDE” With “Supports PIO”

“Transfer Rates to 22 MBytes/sec”

“Individual drive timing for all four IDE devices “

“Concurrent channel operation (PIO & DMA modes) - 4 x 32-Bit Buffer FIFO

per channel”

With

“Concurrent channel operation (PIO modes) - 4 x 32-Bit Buffer FIFO per

channel”

“Support for DMA mode 1 & 2.”

“Support for 11.1/16.6 MB/s, I/O Channel Ready PIO data transfers.”

“Supports 13.3/16.6 MB/s DMA data transfers”

“Bus Master with scatter/gather capability “

“Multi-word DMA support for fast IDE drives “

“Individual drive timing for all four IDE devices “

“Supports both legacy & native IDE modes”

“Supports hard drives larger than 528MB”

“Support for CD-ROM and tape peripherals”

“Backward compatibility with IDE (ATA-1).”

“Drivers for Windows and other OSes”

Issue 1.7 - February 8, 2000

5/48