AD7398 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

生产厂家

AD7398 Datasheet PDF : 24 Pages

| |||

AD7398/AD7399

Parameter

SUPPLY CHARACTERISTICS

Shutdown Supply Current

Positive Supply Current

Negative Supply Current

Power Dissipation

Power Supply Sensitivity

Symbol

IDD_SD

IDD

IDD

ISS

PDISS

PSS

Condition

3 V to 5 V ± 10% ±5 V ± 10%

No load

VIL = 0 V, no load, −40°C < TA < +125°C

VIL = 0 V, no load, −40°C < TA < +85°C

VIL = 0 V, no load

VIL = 0 V, no load

ΔVDD = ±5%

30/60

1.5/2.8

1.5/2.6

1.5/2.5

5

0.006

30/60

1.6/3

1.6/2.8

1.6/2.7

16

0.006

Unit

μA typ/max

mA typ/max

mA typ/max

mA typ/max

mW typ

%/% max

1 One LSB = VREF/4096 V for the 12-bit AD7398.

2 The first eight codes (000H to 007H) are excluded from the linearity error measurement in single-supply operation.

3 These parameters are guaranteed by design and not subject to production testing.

4 When VREF is connected to either the VDD or the VSS power supply, the corresponding VOUT voltage programs between ground and the supply voltage minus the offset

voltage of the output buffer, which is the same as the VZSE error specification. See additional information in the Theory of Operation section.

5 Input resistance is code dependent.

6 Typicals represent average readings measured at 25°C.

7 All input control signals are specified with tR = tF = 2 ns (10% to 90% of 3 V) and timed from a voltage level of 1.5 V.

8 The settling time specification does not apply for negative going transitions within the last 3 LSBs of ground.

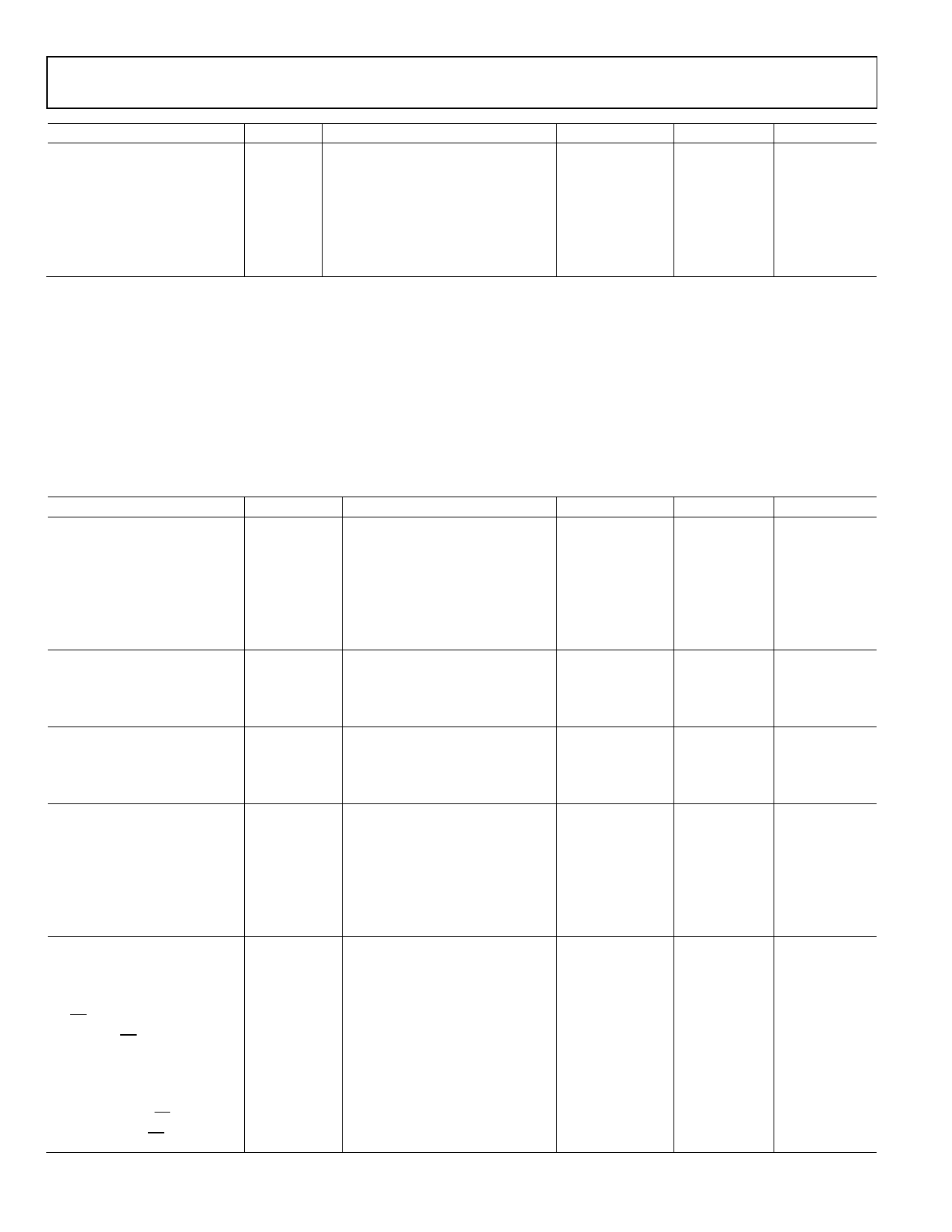

AD7399 10-BIT VOLTAGE OUTPUT DAC

VDD = 5 V, VSS = 0 V; or VDD = +5 V, VSS = –5 V; VREF = +2.5 V, −40°C < TA < +125°C, unless otherwise noted.

Table 2.

Parameter

STATIC PERFORMANCE

Resolution1

Relative Accuracy2

Differential Nonlinearity2

Zero-Scale Error

Full-Scale Voltage Error

Full-Scale Tempco3

REFERENCE INPUT

VREFIN Range4

Input Resistance5

Input Capacitance3

ANALOG OUTPUT

Output Voltage Range

Output Current

Capacitive Load3

LOGIC INPUTS

Logic Input Low Voltage

Logic Input High Voltage

Input Leakage Current

Input Capacitance3

INTERFACE TIMING3, 7

Clock Frequency

Clock Width High

Clock Width Low

CS to Clock Setup

Clock to CS Hold

Load DAC Pulse Width

Data Setup

Data Hold

Load Setup to CS

Load Hold to CS

Symbol

N

INL

DNL

VZSE

VFSE

TCVFS

VREF

RREF

CREF

VOUT

IOUT

CL

VIL

VIH

IIL

CIL

fCLK

tCH

tCL

tCSS

tCSH

tLDAC

tDS

tDH

tLDS

tLDH

Condition

Monotonic

Data = 000H

Data = 3FFH

Data = 155H, worst case

Data = 200H, ΔVOUT = 1 LSB

No oscillation

VDD = 3 V

VDD = 5 V

CLK only

3 V to 5 V ± 10% ±5 V ± 10%

10

10

±1

±1

±1

±1

7

±4

±15

±15

1.5

1.5

0/VDD

40

5

VSS/VDD

40

5

0 to VREF

±5

200

0 to VREF

±5

400

0.5

0.8

0.8

80% VDD

4.0

2.1 to 2.4

2.4

1

1

10

10

11

16.6

45

30

45

30

10

5

20

15

45

30

15

10

10

5

0

0

20

15

Rev. C | Page 4 of 24

Unit

Bits

LSB max

LSB max

mV max

mV max

ppm/°C typ

V min/max

kΩ typ6

pF typ

V

mA typ

pF max

V max

V max

V min

V min

μA max

pF max

MHz max

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min

ns min