SPT2210SCT 查看數據表(PDF) - Signal Processing Technologies

零件编号

产品描述 (功能)

生产厂家

SPT2210SCT Datasheet PDF : 22 Pages

| |||

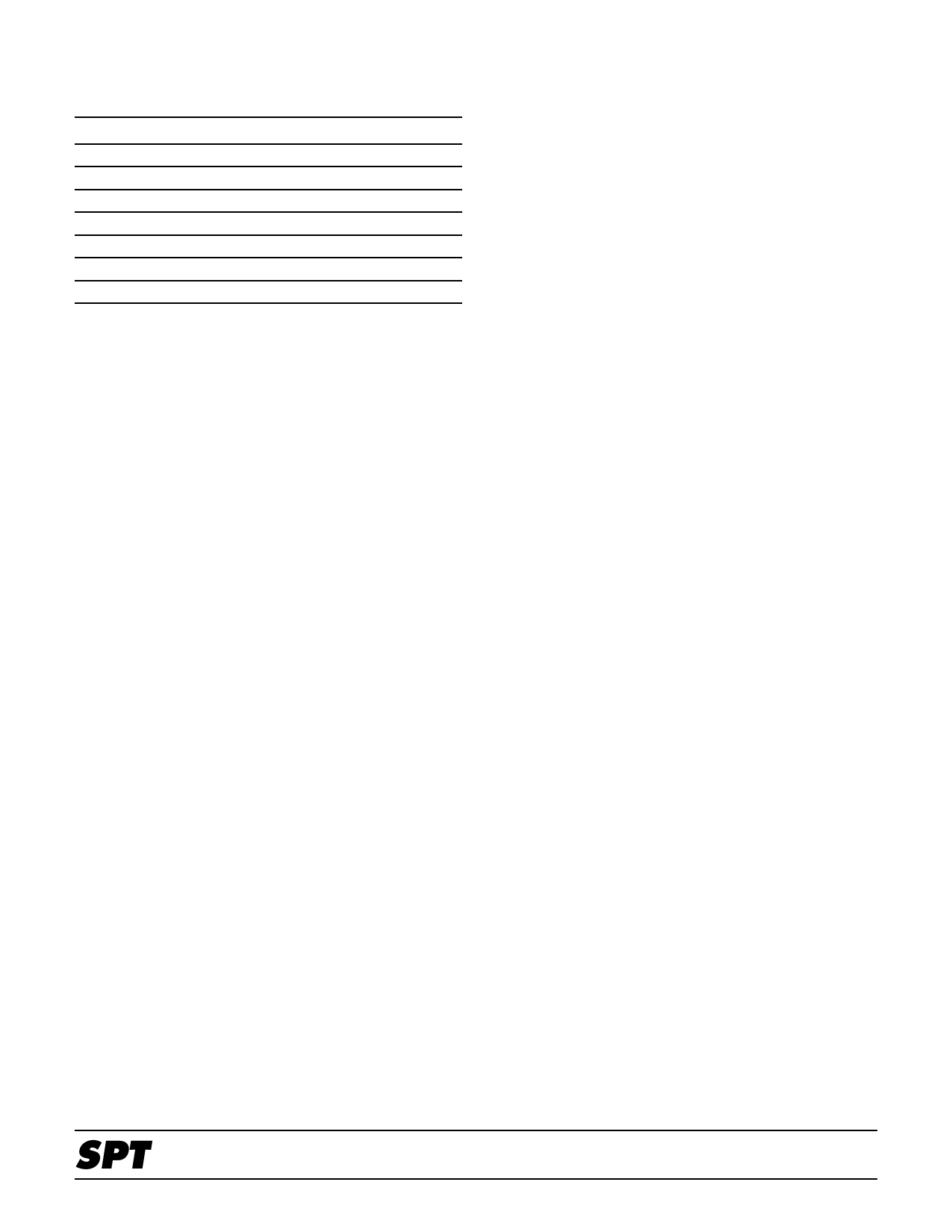

Table IV – Expected Line Clock Count for Various

Modes

Video Mode

NTSC 4Fsc

NTSC Square Pixel

NTSC CCIR 601

PAL 4Fsc

PAL Square Pixel (ƒs = 14.75 MHz)

PAL Square Pixel (ƒs = 12.1875 MHz)

PAL CCIR 601

Clocks

910

780

858

1135

944

780

864

FIELD

This is an input signal controlled by CR5. It is sampled on

the leading edge of the clock cycle. It indicates the field

odd or even and is required in the Blank mode. High level

indicates ODD and low level indicates EVEN field.

TEST

This is an input signal. During normal operation it is set to

a logic low. Test functions of the device are enabled by

taking this pin to a logic high.

SUSPEND

This input pin is set to a logic low for normal operation.

When set to a logic high, the SPT2210 suspends opera-

tion and no output is active. This includes taking in data

from either the MPU data ports or video data.

KEY Pin

This is the external key input pin (TTL level). Input from

this pin is enabled when the external key mode is acti-

vated by setting the command register CR1 bits to D1 = 1

and D0 = 1. (See the Command Register Descriptions

section.) When KEY is high, the colors of the contents of

color lookup table (CLUT) that is specified by means of

GD3...0 are displayed. When KEY is low, the data of

YD7...0 and CD7...0 are output. This mode is called the

external key mode.

GD3...0 Pins

These are the graphic data input pins (TTL level). This

4-bit input port specifies which one of the 16 color entries

in the CLUT is to be output for the current pixel. If GD3...0

is all low when the SPT2210 is in chroma mode, the

CLUT output is transparent and the data of the YD7...0

and CD7...0 ports are output. (This assumes that the

transparent color was not changed in Address 0H of the

CLUT.) Refer to the Color Lookup Table (CLUT) Descrip-

tion section.

VRTENB Pin

This is the vertical interpolation enable signal input pin

(TTL level). When VRTENB is high, vertical interpolation

is enabled and when it is low, vertical interpolation is dis-

abled.

N/C Pins

These are no connect pins.

VIDEO OUTPUTS

Y Pin

This is the luminance or composite analog output signal

pin. The Y output pin is a current source capable of driv-

ing a 75 Ω load terminated to ground to 1 VP-P. The en-

coded analog luminance or composite signal is output on

this pin.

C Pin

This is the chroma analog output signal pin. The C output

pin is a current source capable of driving a 75 Ω load

terminated to ground to 1 VP-P. The chroma signal is out-

put on this pin.

VREF Pin

This is the reference voltage input pin for the internal D/A

converters. A 0.1 µF capacitor and voltage divider of

6.8 kΩ and 5.1 kΩ resistors should be connected to this

pin from +3.3 V.

VCS Pin

This is the control voltage for the output amplitude of the

internal D/A converters. The D/A output amplitude can be

adjusted from 1.0 to 1.4 VP-P using this pin.

MPU INTERFACE AND CLOCK

D7...0 Pins

These are the address and data input/output bus pins

(TTL level). This is a bidirectional 8-bit bus. D7 is the

MSB and D0 is the LSB. When the CS_ (chip select) pin

is high, the D7...0 bus is in a high impedance state.

The SPT2210 features the ability to run without an exter-

nal MPU host. In this mode, D7...0 and RS (Register

Select) pins can be used as external mode setting pins.

The D7...0 pins and RS pin become external setting pins

when CS_, RD_ (Read Enable) and WR_ (Write Enable)

are low for three clock cycles or more. Refer to the Exter-

nal Setting Pin Descriptions section for more details.

CS_ Pin

This is the chip select input pin (TTL level). The SPT2210

is selected for read/write operation when this pin is low.

The CS_ pin is also used in enabling the external pin

mode. Refer to the External Setting Pin Descriptions

section for more details.

SPT

SPT2210

6

8/22/00