MAX3880 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

MAX3880 Datasheet PDF : 12 Pages

| |||

+3.3V, 2.488Gbps, SDH/SONET

1:16 Deserializer with Clock Recovery

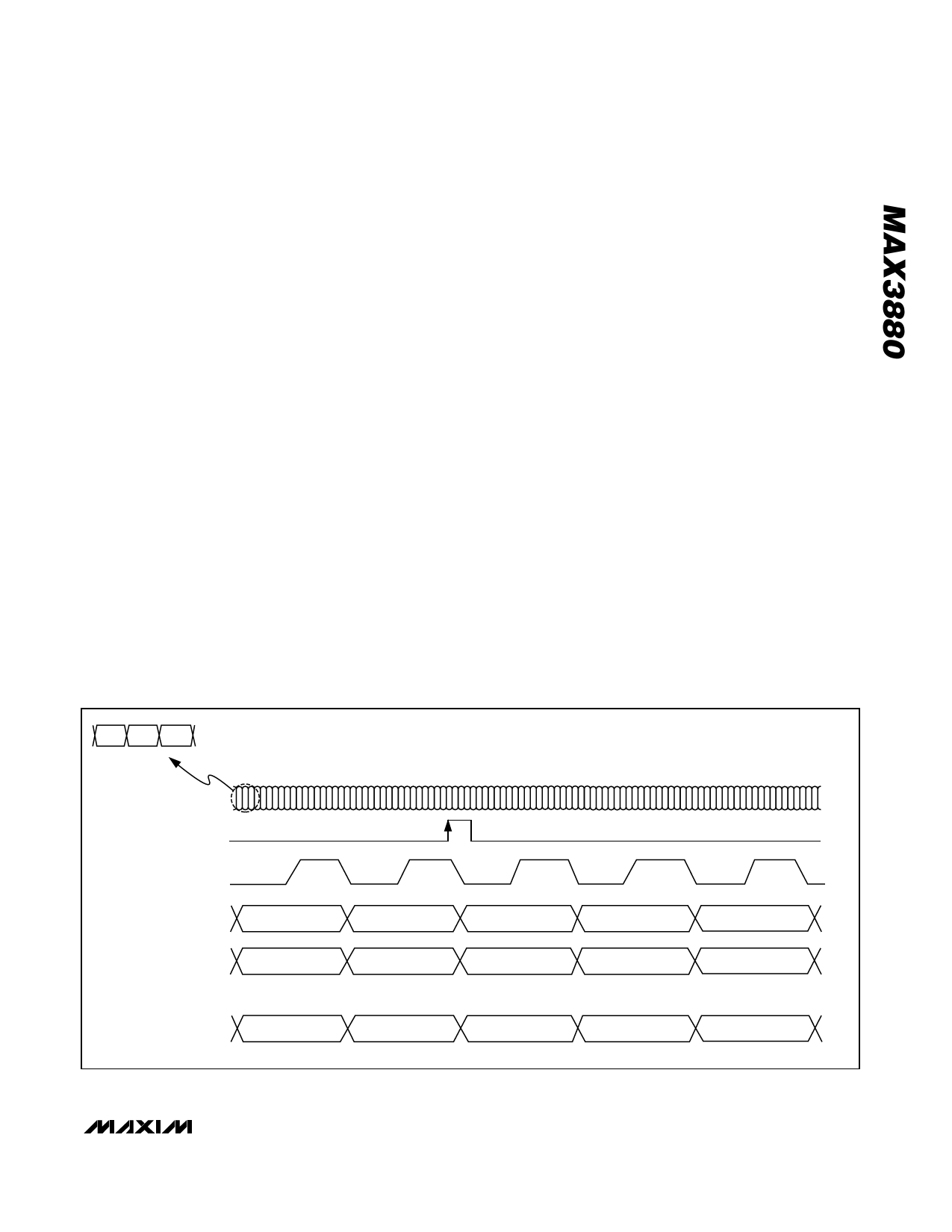

dropped, shifting the alignment between PCLK and

data by 1 bit. The SYNC signal must be at least four

serial bit periods wide (4 x 402ps). See Figure 4 for the

timing diagram and Figure 5 for the timing parameters

diagram.

Input Amplifier

The input amplifiers on both the main data and system

loopback accept a differential input amplitude from

50mVp-p to 800mVp-p. The bit error rate (BER) is bet-

ter than 1 x 10-10 for input signals as small as 9.5mVp-

p, although the jitter tolerance performance will be

degraded. For interfacing with PECL signal levels, see

Applications Information.

Phase Detector

The phase detector in the MAX3880 produces a volt-

age proportional to the phase difference between the

incoming data and the internal clock. Because of its

feedback nature, the PLL drives the error voltage to

zero, aligning the recovered clock to the center of the

incoming data eye for retiming. The external phase

adjust pins (PHADJ+, PHADJ-) allow the user to vary

the internal phase alignment.

Frequency Detector

The digital frequency detector (FD) aids frequency

acquisition during start-up conditions. The frequency

difference between the received data and the VCO

clock is derived by sampling the in-phase and quadra-

ture VCO outputs on both edges of the data input sig-

nal. Depending on the polarity of the frequency

difference, the FD drives the VCO until the frequency

difference is reduced to zero. Once frequency acquisi-

tion is complete, the FD returns to a neutral state. False

locking is completely eliminated by this digital frequen-

cy detector.

Loop Filter and VCO

The phase detector and frequency detector outputs are

summed into the loop filter. A 1.0µF capacitor, CF, is

required to set the PLL damping ratio.

The loop filter output controls the on-chip LC VCO run-

ning at 2.488GHz. The VCO provides low phase noise

and is trimmed to the correct frequency.

Loss-of-Lock Monitor

A loss-of-lock (LOL) monitor is included in the

MAX3880 frequency detector. A loss-of-lock condition

is signaled immediately with a TTL low. When the PLL is

frequency-locked, LOL switches to TTL high in approxi-

mately 800ns.

Note that the LOL monitor is only valid when a data

stream is present on the inputs to the MAX3880. As a

result, LOL does not detect a loss-of-power condition

resulting from a loss of the incoming signal.

D15 D14 D13

SDI

SYNC

PCLK

(LSB) PD0

D0

D16

D32

D48

D65

PD1

D1

D17

•

•

•

(MSB) PD15

D15

D31

TRANSMITTED FIRST

D33

D49

D66

1 BIT HAS SLIPPED

IN THIS TIME SLICE

D47

D64

D80

Figure 4. Timing Diagram

_______________________________________________________________________________________ 7