MAX3882A 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

MAX3882A

MAX3882A Datasheet PDF : 13 Pages

| |||

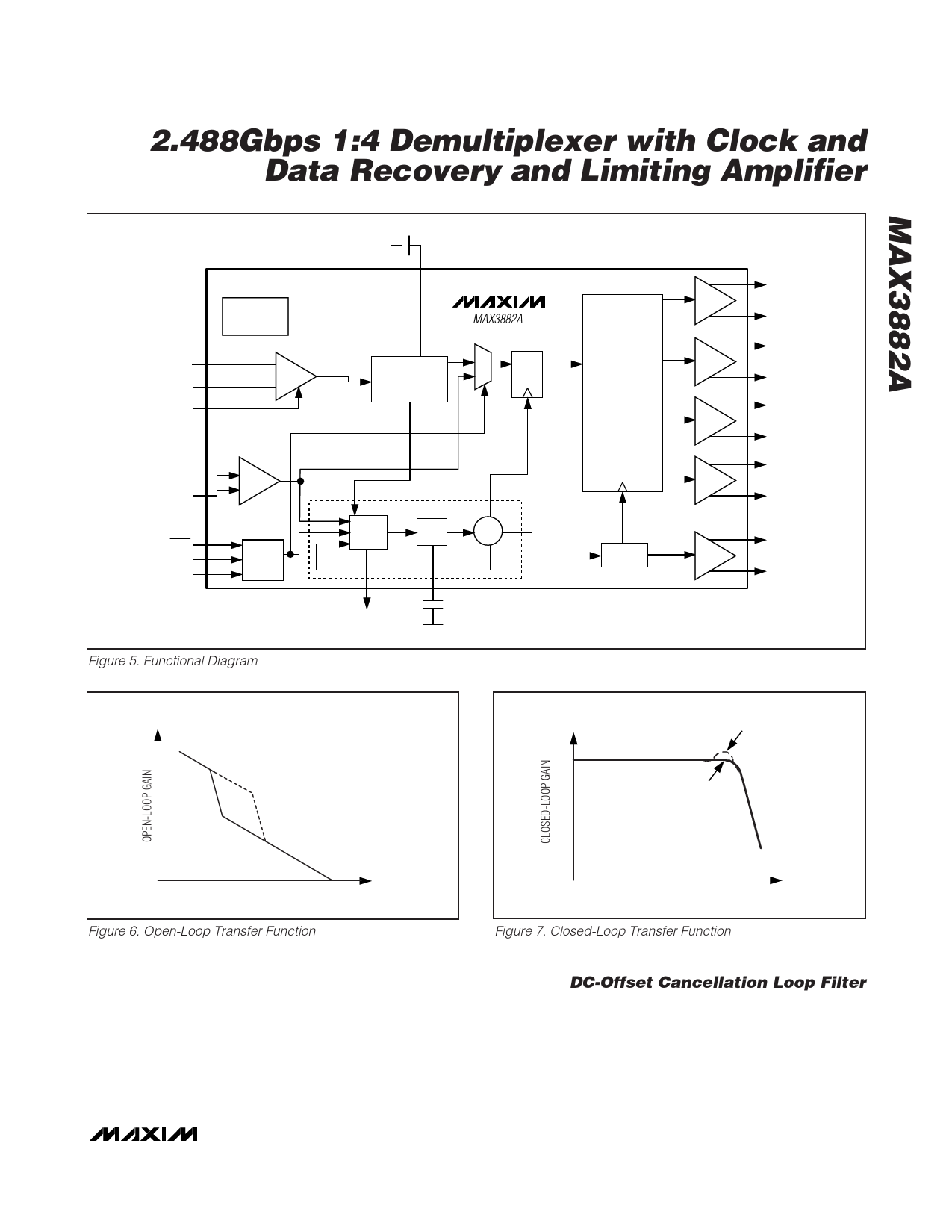

2.488Gbps 1:4 Demultiplexer with Clock and

Data Recovery and Limiting Amplifier

VREF

SDI+

SDI-

VCTRL

BANDGAP

REFERENCE

AMP

SLBI+

SLBI-

LREF

SIS

FREFSET

AMP

LOGIC

Figure 5. Functional Diagram

CAZ

CAZ+

CAZ-

MAX3882A

DC OFFSET

CANCELLATION

0

DQ

1

CK

PFD

LPF

FIL

LOL

VCC

VCO

PLL

LVDS

LVDS

4-BIT

DEMULTIPLEXER

LVDS

LVDS

DIV/4

LVDS

PDO+

PDO-

PD1+

PD1-

PD2+

PD2-

PD3+

PD3-

PCLK+

PCLK-

HO(j2πf) (dB)

CFIL = 0.068μF

fZ = 3.6kHz

CFIL = 0.01μF

fZ = 2.45kHz

1

10

100 1000

Figure 6. Open-Loop Transfer Function

f = (kHz)

HO(j2πf) (dB)

0

-3

CFIL = 0.01μF

CFIL = 0.068μF

1

10

100 1000

Figure 7. Closed-Loop Transfer Function

f = (kHz)

threshold voltage. The +170mV to -170mV threshold

offset can be accomplished by varying the VCTRL volt-

age from 0.3V to 2.1V, respectively. See Figure 2.

When using the VREF to generate voltage for threshold

setting, see Figure 8. Connect VCTRL directly to VCC to

disable threshold adjust.

DC-Offset Cancellation Loop Filter

A DC-offset cancellation loop is implemented to remove

the DC offset of the limiting amplifier. To minimize the

low-frequency pattern-dependent jitter associated with

this DC-cancellation loop, the low-frequency cutoff is

10kHz typical with CAZ = 0.1µF, connected across

CAZ+ and CAZ-.

_______________________________________________________________________________________ 9