MAX4929E 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

MAX4929E Datasheet PDF : 13 Pages

| |||

HDMI 2:1 Low-Frequency Translating Switch

CAPACITANCE

METER

f = 1MHz

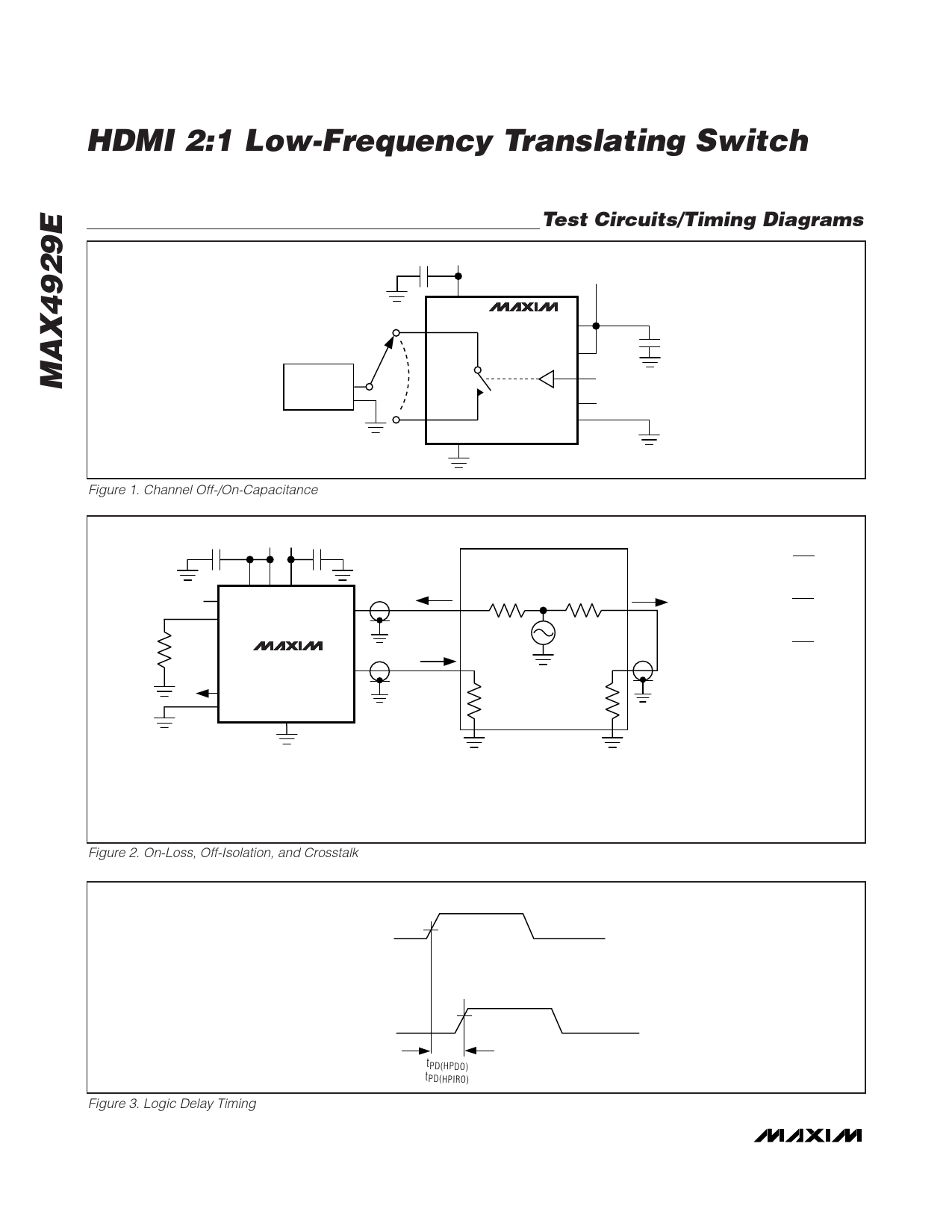

Test Circuits/Timing Diagrams

0.1μF +5V

+3.3V

V+

SDAO/SCLO

MAX4929E VL

CLP

SEL

SDA_/

HIZ1

SCL_

HIZ2

GND

VIL OR VIH

VL

0.1μF

Figure 1. Channel Off-/On-Capacitance

0.1μF

+3.3V +5V 0.1μF

0V OR VL SEL CLP VL V+

VIN

SDAO/

SDA1/

SCLO

SCL1

50Ω

MAX4929E

VOUT

SDA2/

VL

HIZ1

SCL2*

HIZ2

GND

NETWORK

ANALYZER

50Ω

50Ω

MEAS

50Ω

REF

50Ω

MEASUREMENTS ARE STANDARDIZED AGAINST SHORTS AT IC TERMINALS.

OFF-ISOLATION IS MEASURED BETWEEN SDAO/SCLO AND "OFF" SDA_/SCL_ TERMINAL ON EACH SWITCH.

ON-LOSS IS MEASURED BETWEEN SDAO/SCLO AND "ON" SDA_/SCL_ TERMINAL ON EACH SWITCH.

CROSSTALK IS MEASURED FROM ONE CHANNEL TO THE OTHER CHANNEL.

SIGNAL DIRECTION THROUGH SWITCH IS REVERSED; WORST VALUES ARE RECORDED.

Figure 2. On-Loss, Off-Isolation, and Crosstalk

V+ or VL

HPD

50%

HPIR_ 0V

tr < 5ns

tf < 5ns

OFF-ISOLATION

=

20log

VOUT

VIN

ON-LOSS = 20log

VOUT

VIN

CROSSTALK

=

20log

VOUT

VIN

*FOR CROSSTALK THIS PIN IS SCL2.

SCL1 AND SCL0 ARE OPEN.

Figure 3. Logic Delay Timing

HPDO_

HPIRO 0V

VOUT 0.9 x V0UT

tPD(HPDO)

tPD(HPIRO)

4 _______________________________________________________________________________________