OR2C04A ТЪЦуюІТЋИТЊџУАе№╝ѕPDF№╝Ѕ - Lattice Semiconductor

жЏХС╗Ху╝ќтЈи

С║ДтЊЂТЈЈУ┐░ (тіЪУЃй)

ућЪС║Дтјѓт«Х

OR2C04A Datasheet PDF : 192 Pages

| |||

Data Sheet

January 2002

ORCA Series 2 FPGAs

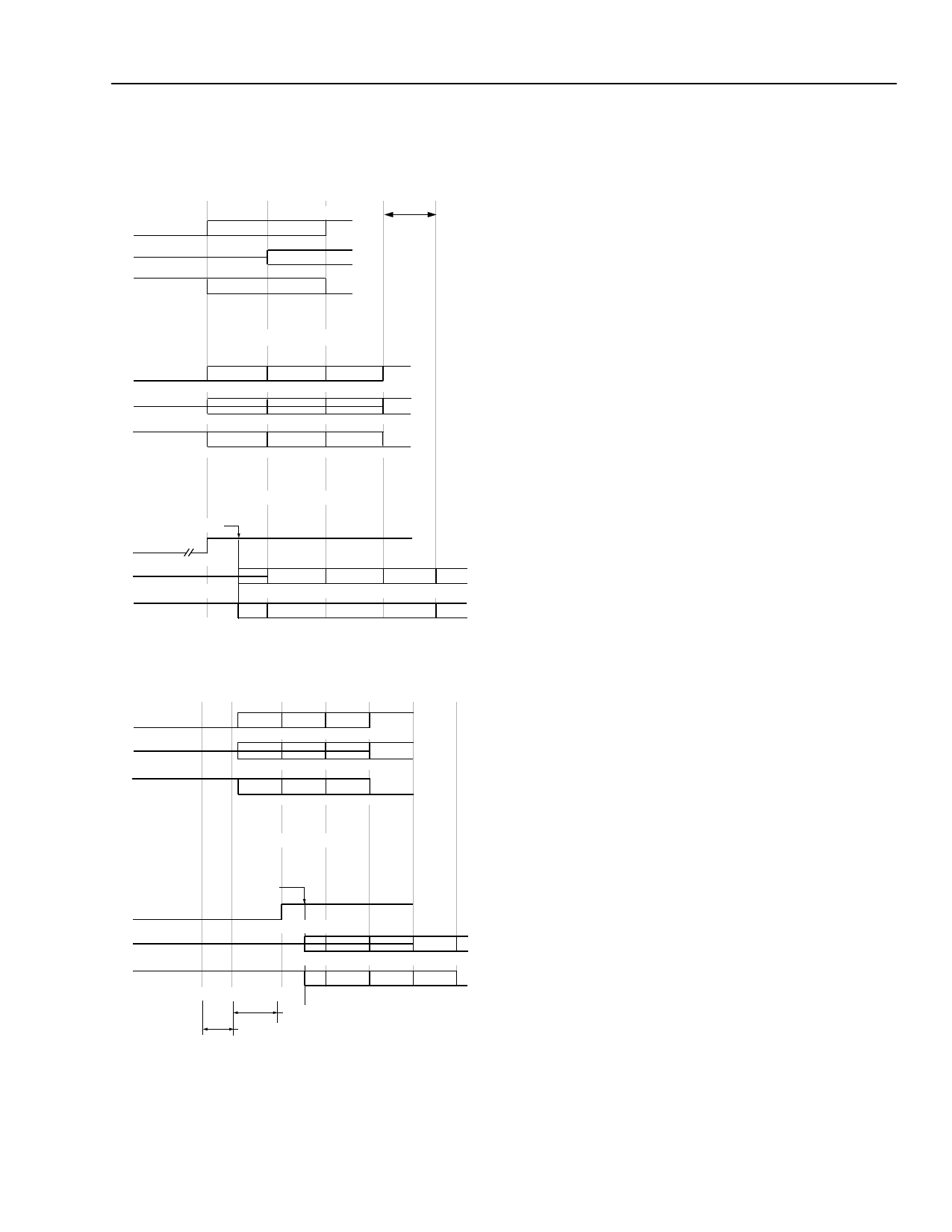

FPGA States of Operation (continued)

DONE

I/O

ATT3000

F

CCLK PERIOD

GLOBAL

RESET

DONE

I/O

GSRN

ACTIVE

ORCA CCLK_NOSYNC

F

C1

C2

C3

C4

C1

C2

C3

C4

C1

C2

C3

C4

ORCA CCLK_SYNC

DONE IN

DONE

C1, C2, C3, OR C4

I/O

Di Di + 1

Di + 2

Di + 3

GSRN

ACTIVE

Di Di + 1

Di + 2

Di + 3

F

Di + 4

Di + 4

UCLK

DONE

I/O

GSRN

ACTIVE

ORCA UCLK_NOSYNC

F

C1 U1

U2

U3

U4

U1

U2

U3

U4

U1

U2

U3

U4

ORCA UCLK_SYNC

Partial Recon№гЂguration

All ORCA device families have been designed to allow

a partial recon№гЂguration of the FPGA at any time. This

is done by setting a bit stream option in the previous

con№гЂguration sequence that tells the FPGA to not reset

all of the con№гЂguration RAM during a recon№гЂguration.

Then only the con№гЂguration frames that are to be modi-

№гЂed need to be rewritten, thereby reducing the con№гЂgu-

ration time.

Other bit stream options are also available that allow

one portion of the FPGA to remain in operation while a

partial recon№гЂguration is being done. If this is done, the

user must be careful to not cause contention between

the two con№гЂgurations (the bit stream resident in the

FPGA and the partial recon№гЂguration bit stream) as the

second recon№гЂguration bit stream is being loaded.

Other Con№гЂguration Options

Con№гЂguration options used during device start-up were

previously discussed in the FPGA States of Operation

section of this data sheet. There are many other con№гЂg-

uration options available to the user that can be set

during bit stream generation in ORCA Foundry. These

include options to enable boundary scan, readback

options, and options to control and use the internal

oscillator after con№гЂguration.

Other useful options that affect the next con№гЂguration

(not the current con№гЂguration process) include options

to disable the global set/reset during con№гЂguration, dis-

able the 3-state of I/Os during con№гЂguration, and dis-

able the reset of internal RAMs during con№гЂguration to

allow for partial con№гЂgurations (see above). For more

information on how to set these and other con№гЂguration

options, please see the ORCA Foundry documenta-

tion.

DONE IN

DONE

C1 U1, U2, U3, OR U4

F

I/O

Di Di + 1 Di + 2 Di + 3 Di + 4

GSRN

ACTIVE

Di Di + 1 Di + 2 Di + 3

UCLK PERIOD

SYNCHRONIZATION UNCERTAINTY

F = finished, no more CLKs required.

5-2761(F).r4

Figure 38. Start-Up Waveforms

Con№гЂguration Data Format

The ORCA Foundry Development System interfaces

with front-end design entry tools and provides the tools

to produce a fully con№гЂgured FPGA. This section dis-

cusses using the ORCA Foundry Development System

to generate con№гЂguration RAM data and then provides

the details of the con№гЂguration frame format.

The ORCA Series 2 series of FPGAs are enhanced

versions of the ORCA ATT2Cxx/ATT2Txx architectures

that provide upward bit stream compatibility for both

series of devices as well as with each other.

Lattice Semiconductor

43