VSC7216-01 查看數據表(PDF) - Vitesse Semiconductor

零件编号

产品描述 (功能)

生产厂家

VSC7216-01 Datasheet PDF : 38 Pages

| |||

VITESSE

SEMICONDUCTOR CORPORATION

Multi-Gigabit Interconnect Chip

Multi-Gigabit Interconnect Chip

Preliminary Data Sheet

VSCV7S2C1672-0116

Encoder Bypass Mode

When ENDEC is LOW, the 8B/10B encoders are bypassed and a 10-bit input character Tn(7:0) is serialized

directly in each channel, bit Tn0 is transmitted first. The C/Dn input becomes Tn8, and WSENn becomes Tn9.

The KCHAR input becomes ENCDET which is not used in the transmitter, but when HIGH, enables Comma

detection in all four receivers. Refer to the Decoder Bypass Mode section for a description of this mode of

operation in the receiver. The latency through the transmitter is reduced by one character time when ENDEC is

LOW. This mode of operation is similar to a 10-bit interface commonly found in serializer/deserializers for the

Fibre Channel ( VSC7125) and Gigabit Ethernet markets (VSC7135).

Word Sync Generation

The VSC7216-01 can perform channel alignment (also referred to as “word alignment” or “word sync”),

meaning that the four receive data output streams are aligned such that the same 4-byte word presented to the

four transmit channel inputs for serialization will be transferred on the receive channel parallel outputs. The

Word Sync Sequence provides a unique synchronization point in the serial data stream that is used to align the

receive channels. This sequence consists of 16 consecutive K28.5 IDLE characters with disparity reversals on

the second and fourth characters. The Word Sync Sequence is sent either as “I+ I+ I- I- I+ I- I+ I- I+ I- I+ I- I+

I- I+ I-” or as “I- I- I+ I+ I- I+ I- I+ I- I+ I- I+ I- I+ I- I+”, depending on the transmitter’s running disparity at the

time the first IDLE character is serialized.

Transmission of the Word Sync Sequence is initiated independently in each channel when the WSENn

input is asserted HIGH for one character time (see Figure 5). When WSENn is HIGH, the C/Dn and Tn(7:0)

inputs are ignored. The WSENn, C/Dn and Tn(7:0) inputs are also ignored for the subsequent 15 character

times. In Figure 5, the Word Sync Sequence is initiated in cycle W1 and transmitted through cycle W16.

Normal data transmission (or the transmission of another Word Sync Sequence) resumes in cycle D3. This

figure is illustrated assuming that input timing is referenced to REFCLK (e.g., TMODE(2:0)=000) with the

DUAL input LOW. As long as WSENn remains asserted, another Word Sync Sequence will be generated.

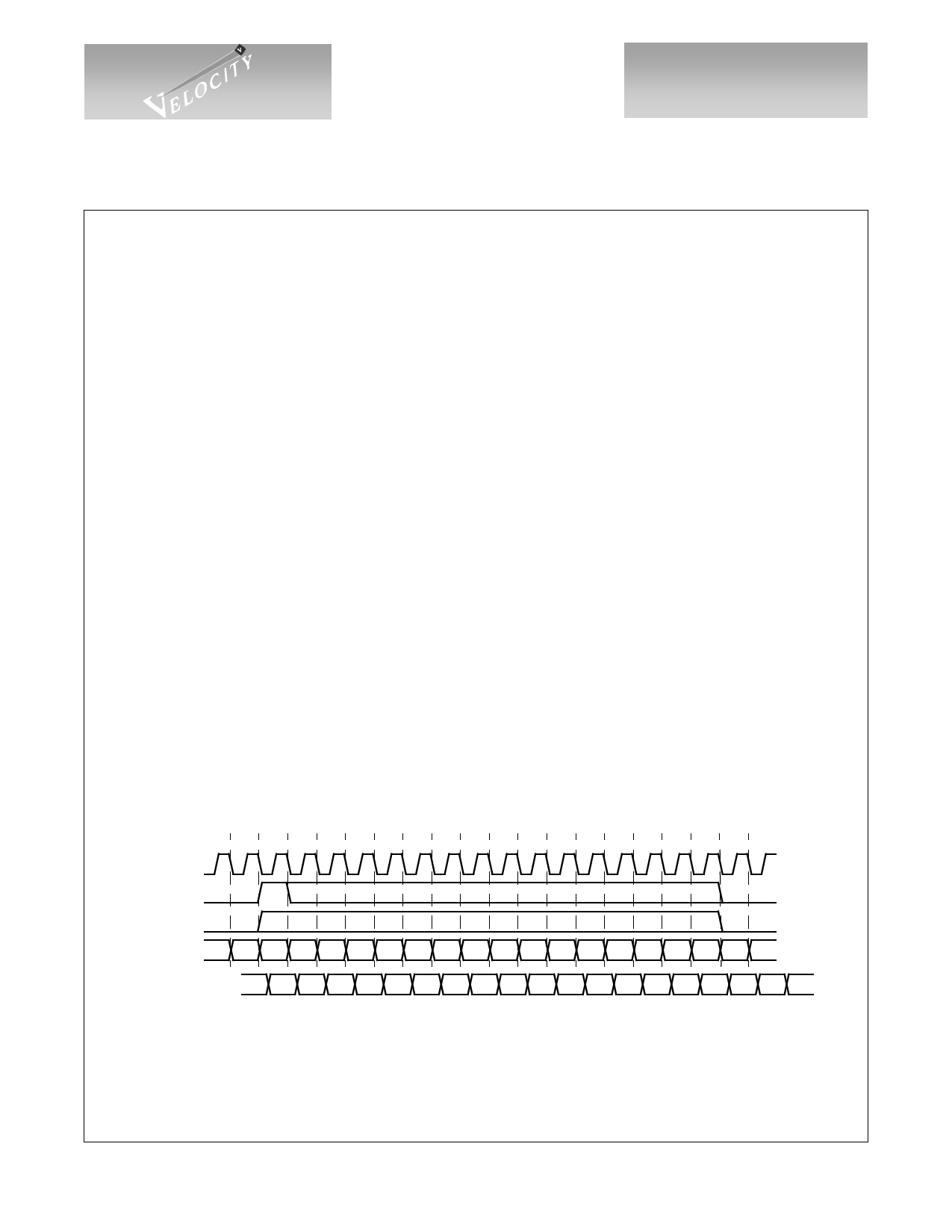

Figure 5: Word Sync Sequence Generation

D1 D2 W1 W2 W3 W4 W5 W6 W7 W8 W9 W10 W11 W12 W13 W14 W15 W16 D3 D4

REFCLK

WSENn

C/Dn

Tn(7:0) 0x01 0x02 XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX XX 0x03 0x04

TXn+/-

D1.0+ D2.0+ K28.5+ K28.5+ K28.5- K28.5- K28.5+ K28.5- K28.5+ K28.5- K28.5+ K28.5- K28.5+ K28.5- K28.5+ K28.5- K28.5+ K28.5- D3.0+ D4.0-

Page 6

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

G52352-0, Rev 3.2

05/05/01