Z53C80 查看數據表(PDF) - Zilog

零件编号

产品描述 (功能)

生产厂家

Z53C80 Datasheet PDF : 40 Pages

| |||

ZILOG

D7

D0

0X 0 1X 0XX

/ACK

/ATN

Busy Error

Phase Match

Interrupt Request Active

Parity Error

DMA Request

End of DMA

D7

D0

0X 1 1 1 0XX

Z53C80 SCSI

/ACK

/ATN

Busy Error

Phase Match

Interrupt Request Active

Parity Error

DMA Request

End of DMA

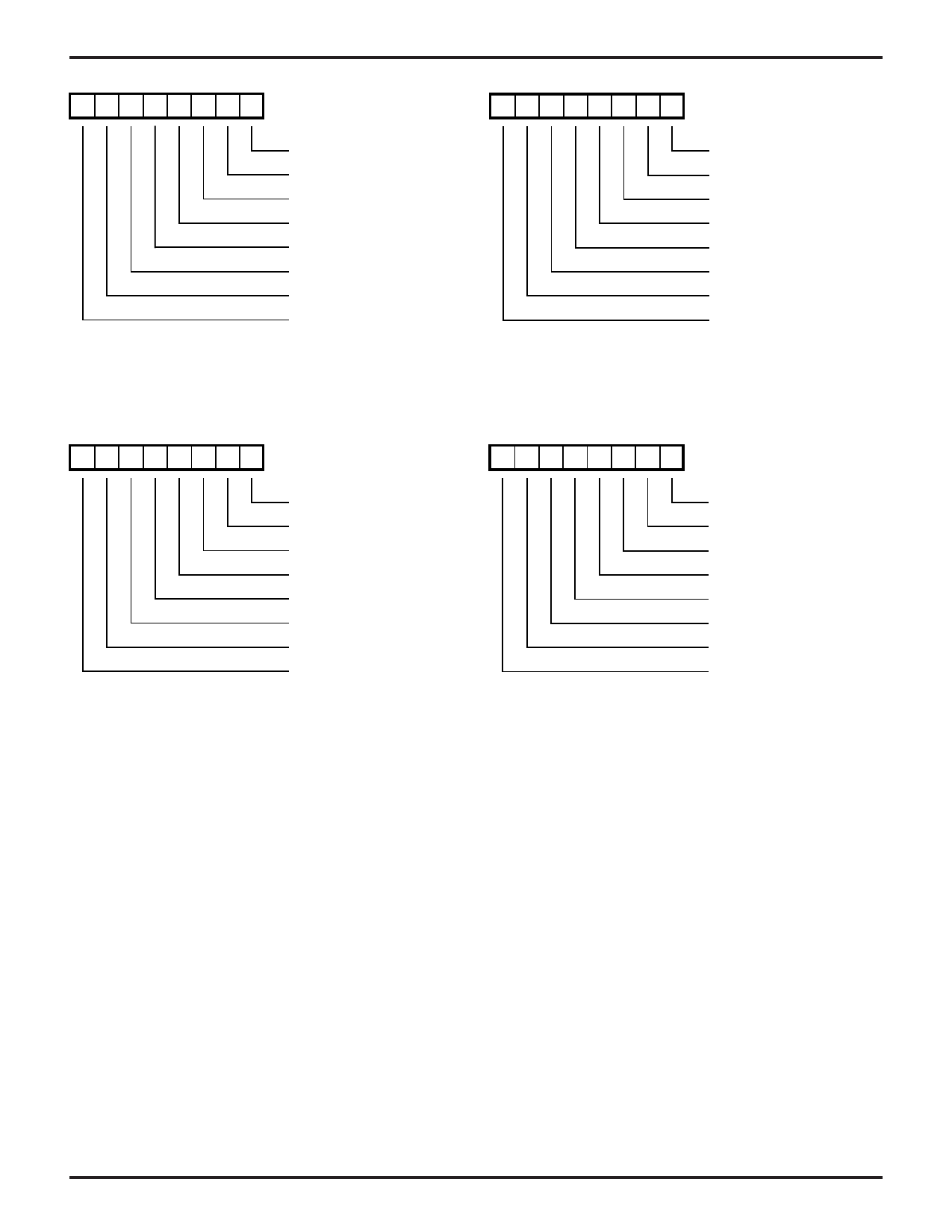

Figure 19. Bus and Status Register

D7

D0

XXXXXXXX

/DBP

/SEL

I//O

C//D

/MSG

/REQ

/BSY

/RST

Figure 21. Bus and Status Register

D7

D0

0 1 1XXX 0X

/DBP

/SEL

I//O

C//D

/MSQ

/REQ

/BSY

/RST

Figure 20. Current SCSI Bus Status Register

Figure 22. Current SCSI Bus Status Register

Parity Error. An interrupt is generated for a received parity

error it the Enable Parity Check (bit 5) and the Enable Parity

Interrupt (bit 4) bits are set (1) in the Mode Register. Parity

is checked during a read of the Current SCSI Data Register

and during a DMA receive operation. A parity error can be

detected without generating an interrupt by disabling the

Enable Parity Interrupt bit and checking the Parity Error

flag (Bus and Status Register, bit 5).

The proper values for the Bus and Status Register and the

Current SCSI Bus Status Register are displayed in Figures

21 and 22, respectively.

Bus Phase Mismatch. The SCSI phase lines have the

signals I//O, C//D, and /MSG. These signals are compared

with the corresponding bits in the Target Command

Register: Assert I//O (bit 0), Assert C//D (bit 1), and Assert

/MSG (bit 2). The comparison occurs continually and is

reflected in the Phase Match bit (bit 3) of the Bus and Status

Register. If the DMA Mode bit (Mode Register, bit 1) is

active and a phase mismatch occurs when /REQ transitions

from False to True, an interrupt (IRQ) is generated.

PS97SCC0200

15