M24164-WMN1T жҹҘзңӢж•ёж“ҡиЎЁпјҲPDFпјү - STMicroelectronics

йӣ¶д»¶зј–еҸ·

дә§е“ҒжҸҸиҝ° (еҠҹиғҪ)

з”ҹдә§еҺӮ家

M24164-WMN1T

M24164-WMN1T Datasheet PDF : 21 Pages

| |||

M24164

DEVICE OPERATION

The device supports the I2C protocol. This is sum-

marized in Figure 2. Any device that sends data on

to the bus is defined to be a transmitter, and any

device that reads the data to be a receiver. The

device that controls the data transfer is known as

the bus master, and the other as the slave device.

A data transfer can only be initiated by the bus

master, which will also provide the serial clock for

synchronization. The M24164 device is always a

slave in all communication.

Start Condition

Start is identified by a falling edge of Serial Data

(SDA) while Serial Clock (SCL) is stable in the

High state. A Start condition must precede any

data transfer command. The device continuously

monitors (except during a Write cycle) Serial Data

(SDA) and Serial Clock (SCL) for a Start condition,

and will not respond unless one is given.

Stop Condition

Stop is identified by a rising edge of Serial Data

(SDA) while Serial Clock (SCL) is stable and driv-

en High. A Stop condition terminates communica-

tion between the device and the bus master. A

Read command that is followed by NoAck can be

followed by a Stop condition to force the device

into the Stand-by mode. A Stop condition at the

end of a Write command triggers the internal EE-

PROM Write cycle.

Acknowledge Bit (ACK)

The acknowledge bit is used to indicate a success-

ful byte transfer. The bus transmitter, whether it be

bus master or slave device, releases Serial Data

(SDA) after sending eight bits of data. During the

9th clock pulse period, the receiver pulls Serial

Data (SDA) Low to acknowledge the receipt of the

eight data bits.

Data Input

During data input, the device samples Serial Data

(SDA) on the rising edge of Serial Clock (SCL).

For correct device operation, Serial Data (SDA)

must be stable during the rising edge of Serial

Clock (SCL), and the Serial Data (SDA) signal

must change only when Serial Clock (SCL) is driv-

en Low.

Memory Addressing

To start communication between the bus master

and the slave device, the bus master must initiate

a Start condition. Following this, the bus master

sends eight bits, on Serial Data (SDA), most signif-

icant bit first. These consist of the 7-bit Device Se-

lect Code, and the Read/Write bit (RW), as shown

in Table 2. This last bit is set to 1 for Read, and 0

for Write operations.

The Device Select Code contains the three most

significant bits of the address within the memory

(A10, A9, A8), and a 3-bit Chip Enable вҖңAddressвҖқ

(E2, E1, E0).

When the Device Select Code is received on Seri-

al Data (SDA), the device only responds if the Chip

Enable Address is the same as the value on the

Chip Enable (E0, E2, and the inverse of E1) in-

puts. Up to eight devices can be connected on the

same bus, giving a total memory capacity of

128 Kbits, 16 KBytes.

If a match occurs on the Device Select code, the

corresponding device gives an acknowledgment

on Serial Data (SDA) during the 9th bit time. If the

device does not match the Device Select code, it

deselects itself from the bus, and goes into Stand-

by mode.

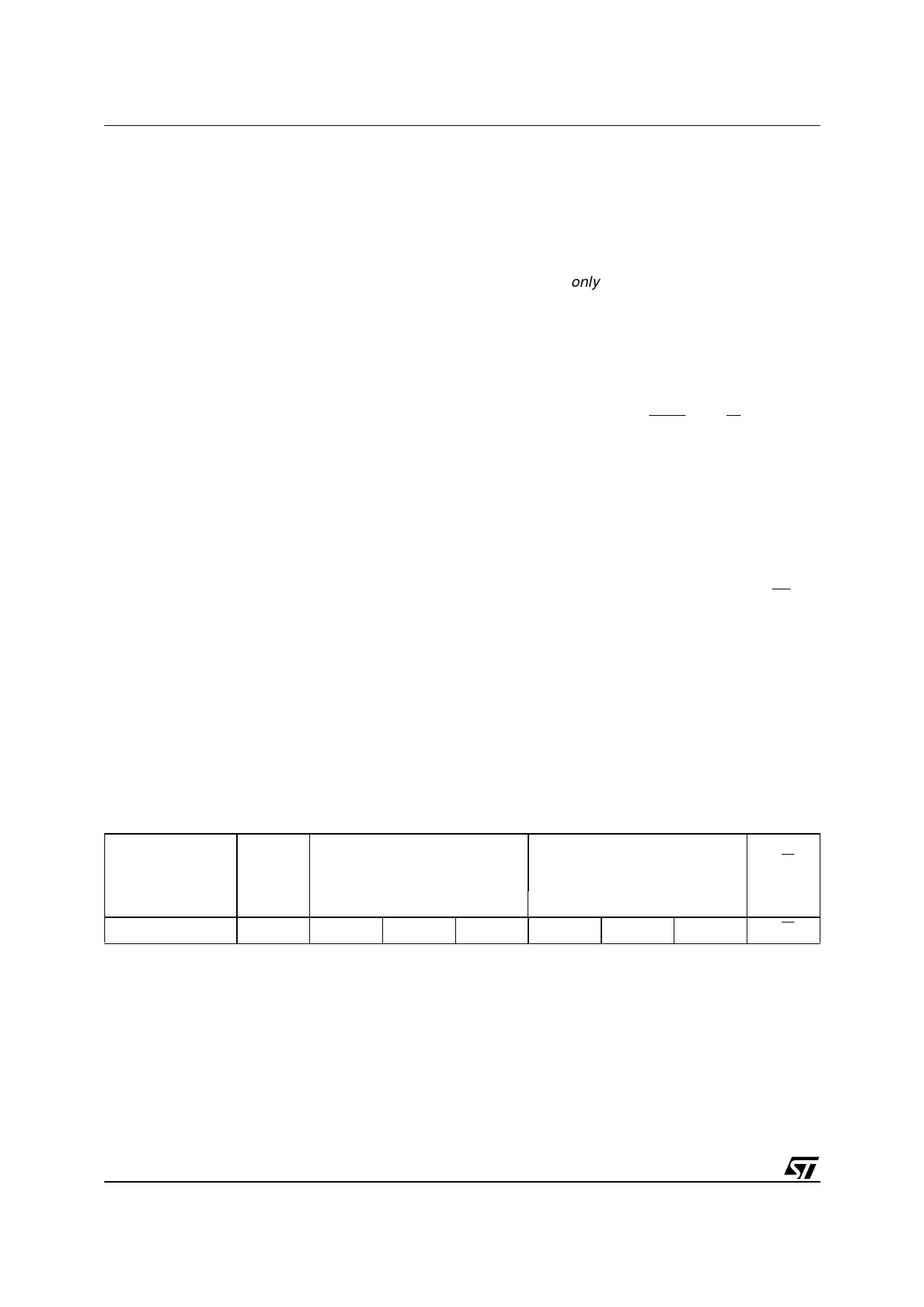

Table 2. Device Select Code 1

Device

Type

Identifier

Chip Enable Address

Most Significant Address Bits

RW

b7

b6

b5

b4

b3

b2

b1

b0

Device Select Code

1

E2

E1

E0

A10

A9

A8

RW

Note: 1. The most significant bit, b7, is sent first.

4/21