FOD2200S(2004) 查看數據表(PDF) - Fairchild Semiconductor

零件编号

产品描述 (功能)

生产厂家

FOD2200S Datasheet PDF : 14 Pages

| |||

LOW INPUT CURRENT

LOGIC GATE OPTOCOUPLERS

FOD2200

NOTES

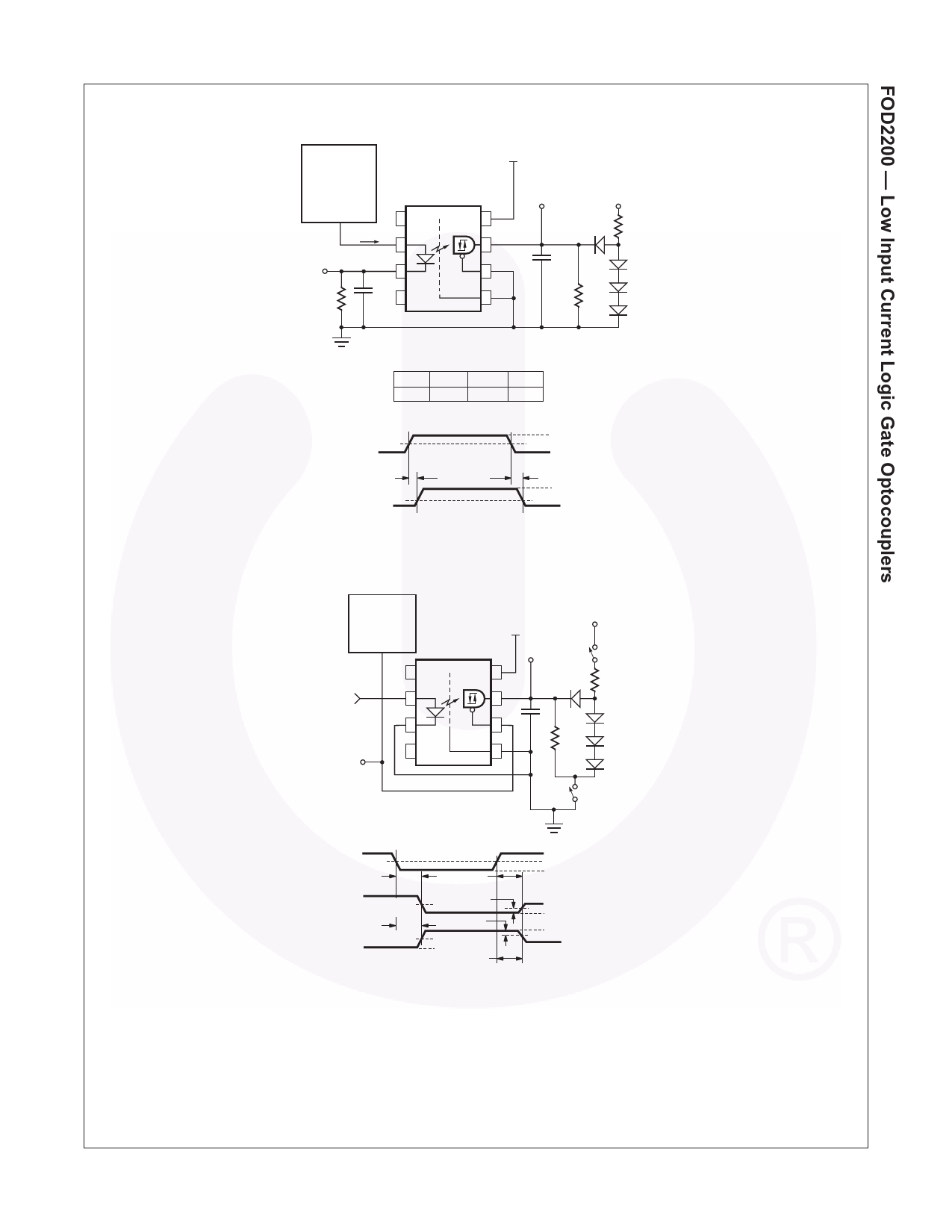

1. The VCC supply to each optoisolator must be bypassed by a 0.1µF capacitor or larger. This can be either a ceramic or solid

tantalum capacitor with good high frequency characteristic and should be connected as close as possible to the package VCC

and GND pins of each device.

2. tPLH - Propagation delay is measured from the 50% level on the LOW to HIGH transition of the input current pulse to the

1.3V level on the LOW to HIGH transition of the output voltage pulse.

3. tPHL - Propagation delay is measured from the 50% level on the HIGH to LOW transition of the input current pulse to the 1.3V

level on the HIGH to LOW transition of the output voltage pulse.

4. When the peaking capacitor is omitted, propagation delay times may increase by 100 ns.

5. tr - Rise time is measured from the 10% to the 90% levels on the LOW to HIGH transition of the output pulse.

6. tf - Fall time is measured from the 90% to the 10% levels on the HIGH to LOW transition of the output pulse.

7. CMH - The maximum tolerable rate of fall of the common mode voltage to ensure the output will remain in the high state (i.e.,

VOUT > 2.0 V).

8. CML - The maximum tolerable rate of rise of the common mode voltage to ensure the output will remain in the low state (i.e.,

VOUT < 0.8 V).

9. Device considered a two-terminal device: Pins 1,2,3 and 4 shorted together, and Pins 5,6,7 and 8 shorted together.

10. Duration of output short circuit time should not exceed 10 ms.

© 2004 Fairchild Semiconductor Corporation

Page 5 of 14

7/7/04