LCMXO640E-3T144IES 查看數據表(PDF) - Lattice Semiconductor

零件编号

产品描述 (功能)

生产厂家

LCMXO640E-3T144IES Datasheet PDF : 95 Pages

| |||

MachXO Family Data Sheet

Introduction

August 2006

Data Sheet DS1002

Features

■ Non-volatile, Infinitely Reconfigurable

• Instant-on – powers up in microseconds

• Single chip, no external configuration memory

required

• Excellent design security, no bit stream to

intercept

• Reconfigure SRAM based logic in milliseconds

• SRAM and non-volatile memory programmable

through JTAG port

• Supports background programming of

non-volatile memory

■ Sleep Mode

• Allows up to 100x static current reduction

■ TransFR™ Reconfiguration (TFR)

• In-field logic update while system operates

■ High I/O to Logic Density

• 256 to 2280 LUT4s

• 73 to 271 I/Os with extensive package options

• Density migration supported

• Lead free/RoHS compliant packaging

■ Embedded and Distributed Memory

• Up to 27.6 Kbits sysMEM™ Embedded Block

RAM

• Up to 7.5 Kbits distributed RAM

• Dedicated FIFO control logic

■ Flexible I/O Buffer

• Programmable sysIO™ buffer supports wide

range of interfaces:

− LVCMOS 3.3/2.5/1.8/1.5/1.2

− LVTTL

− PCI

− LVDS, Bus-LVDS, LVPECL, RSDS

■ sysCLOCK™ PLLs

• Up to two analog PLLs per device

• Clock multiply, divide, and phase shifting

■ System Level Support

• IEEE Standard 1149.1 Boundary Scan

• Onboard oscillator

• Devices operate with 3.3V, 2.5V, 1.8V or 1.2V

power supply

• IEEE 1532 compliant in-system programming

Introduction

The MachXO is optimized to meet the requirements of

applications traditionally addressed by CPLDs and low

capacity FPGAs: glue logic, bus bridging, bus interfac-

ing, power-up control, and control logic. These devices

bring together the best features of CPLD and FPGA

devices on a single chip.

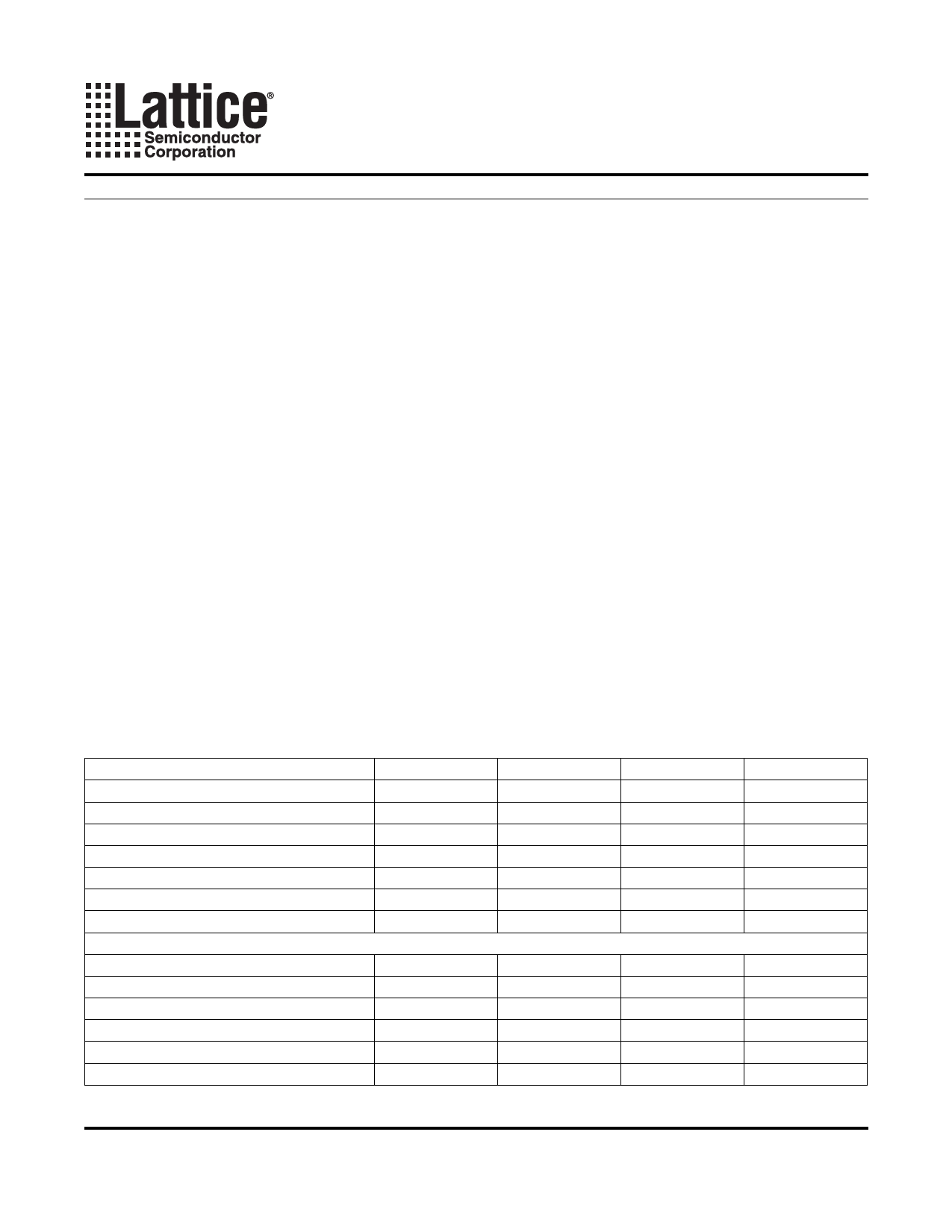

Table 1-1. MachXO Family Selection Guide

Device

LCMXO256

LUTs

256

Dist. RAM (Kbits)

2.0

EBR SRAM (Kbits)

0

Number of EBR SRAM Blocks (9 Kbits)

0

VCC Voltage

Number of PLLs

1.2/1.8/2.5/3.3V

0

Max. I/O

78

Packages

100-pin TQFP (14x14 mm)

78

144-pin TQFP (20x20 mm)

100-ball csBGA (8x8 mm)

78

132-ball csBGA (8x8 mm)

256-ball ftBGA (17x17 mm)

324-ball ftBGA (19x19 mm)

LCMXO640

640

6.0

0

0

1.2/1.8/2.5/3.3V

0

159

74

113

74

101

159

LCMXO1200

1200

6.25

9.2

1

1.2/1.8/2.5/3.3V

1

211

73

113

101

211

LCMXO2280

2280

7.5

27.6

3

1.2/1.8/2.5/3.3V

2

271

73

113

101

211

271

© 2006 Lattice Semiconductor Corp. All Lattice trademarks, registered trademarks, patents, and disclaimers are as listed at www.latticesemi.com/legal. All other brand

or product names are trademarks or registered trademarks of their respective holders. The specifications and information herein are subject to change without notice.

www.latticesemi.com

1-1

DS1002 Introduction_01.3