AD7453BRT-REEL7 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

生产厂家

AD7453BRT-REEL7 Datasheet PDF : 20 Pages

| |||

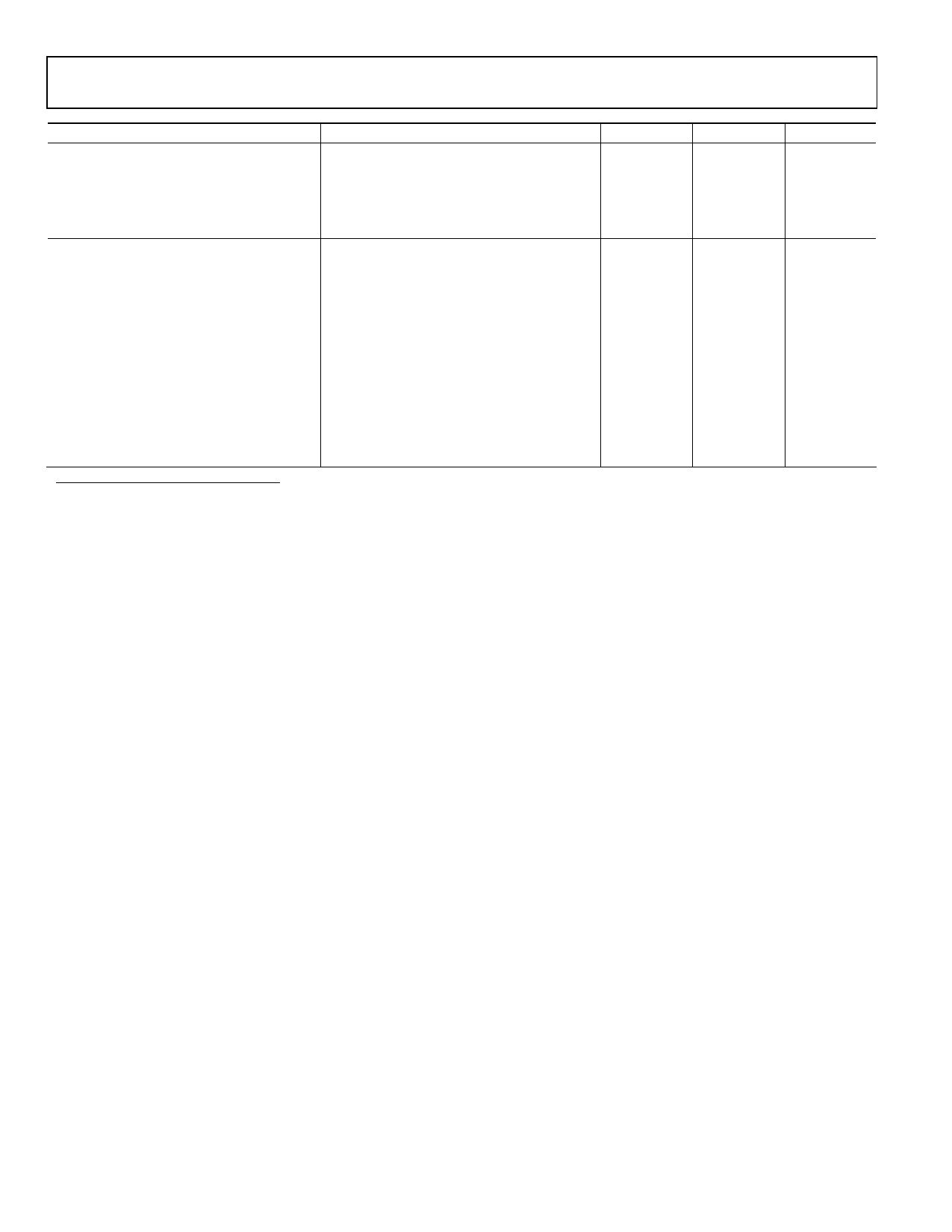

AD7453

Parameter

CONVERSION RATE

Conversion Time

Track-and-Hold Acquisition Time2

Throughput Rate

POWER REQUIREMENTS

VDD

IDD7, 8

Normal Mode (Static)

Normal Mode (Operational)

Full Power-Down Mode

Power Dissipation

Normal Mode (Operational)

Full Power-Down Mode

Test Conditions/Comments

1.6 µs with a 10 MHz SCLK

Sine wave input

Full-scale step input

SCLK on or off

VDD = 4.75 V to 5.25 V

VDD= 2.7 V to 3.6 V

SCLK on or off

VDD = 5 V; 1.55 mW typ for 100 kSPS7

VDD = 3 V; 0.64 mW typ for 100 kSPS7

VDD = 5 V; SCLK on or off

VDD = 3 V; SCLK on or off

A Version1 B Version1 Unit

16

16

SCLK cycles

250

250

ns max

290

290

ns max

555

555

kSPS max

2.7/5.25

2.7/5.25

V min/max

0.5

0.5

mA typ

1.5

1.5

mA max

1.2

1.2

mA max

1

1

µA max

7.25

7.25

mW max

3.3

3.3

mW max

5

5

µW max

3

3

µW max

1 Temperature ranges as follows: A, B versions: –40°C to +85°C.

2 See Terminology section.

3 Analog inputs with slew rates exceeding 27 V/µs (full-scale input sine wave > 3.5 MHz) within the acquisition time may cause an incorrect result to be returned by the

converter.

4 A small dc input is applied to VIN– to provide a pseudo ground for VIN+.

5 The AD7453 is functional with a reference input in the range 100 mV to VDD.

6 Guaranteed by characterization.

7 See Power vs. Throughput Rate section.

8 Measured with a full-scale dc input.

Rev. B | Page 4 of 20