MFRC52202HN1 查看數據表(PDF) - NXP Semiconductors.

零件编号

产品描述 (功能)

生产厂家

MFRC52202HN1 Datasheet PDF : 95 Pages

| |||

NXP Semiconductors

MFRC522

Standard performance MIFARE and NTAG frontend

8.1.2.2 SPI write data

To write data to the MFRC522 using SPI requires the byte order shown in Table 7. It is

possible to write up to n data bytes by only sending one address byte.

The first send byte defines both the mode and the address byte.

Table 7. MOSI and MISO byte order

Line

Byte 0

Byte 1

Byte 2

To

MOSI

address 0 data 0

data 1

...

MISO

X[1]

X[1]

X[1]

...

[1] X = Do not care.

Remark: The MSB must be sent first.

Byte n

data n 1

X[1]

Byte n + 1

data n

X[1]

8.1.2.3 SPI address byte

The address byte must meet the following format.

The MSB of the first byte defines the mode used. To read data from the MFRC522 the

MSB is set to logic 1. To write data to the MFRC522 the MSB must be set to logic 0. Bits 6

to 1 define the address and the LSB is set to logic 0.

Table 8. Address byte 0 register; address MOSI

7 (MSB) 6

5

4

3

2

1

0 (LSB)

1 = read address

0

0 = write

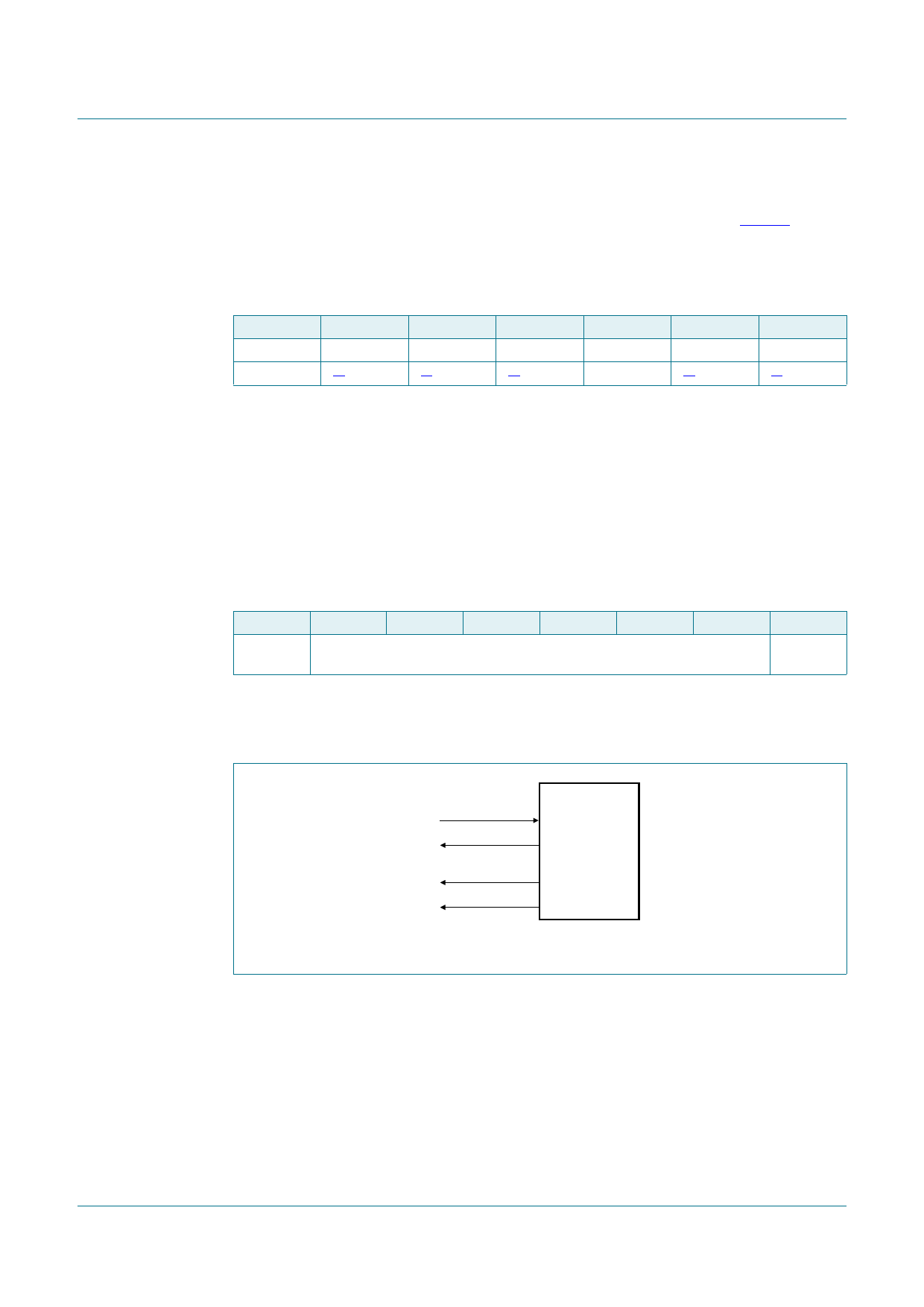

8.1.3 UART interface

8.1.3.1 Connection to a host

MFRC522

RX

RX

TX

TX

DTRQ

MX

DTRQ

MX

001aak587

Fig 8. UART connection to microcontrollers

Remark: Signals DTRQ and MX can be disabled by clearing TestPinEnReg register’s

RS232LineEn bit.

MFRC522

Product data sheet

COMPANY PUBLIC

All information provided in this document is subject to legal disclaimers.

Rev. 3.9 — 27 April 2016

112139

© NXP Semiconductors N.V. 2016. All rights reserved.

11 of 95