73K224BL-IHR/F 查看數據表(PDF) - Teridian Semiconductor Corporation

零件编号

产品描述 (功能)

生产厂家

73K224BL-IHR/F

73K224BL-IHR/F Datasheet PDF : 33 Pages

| |||

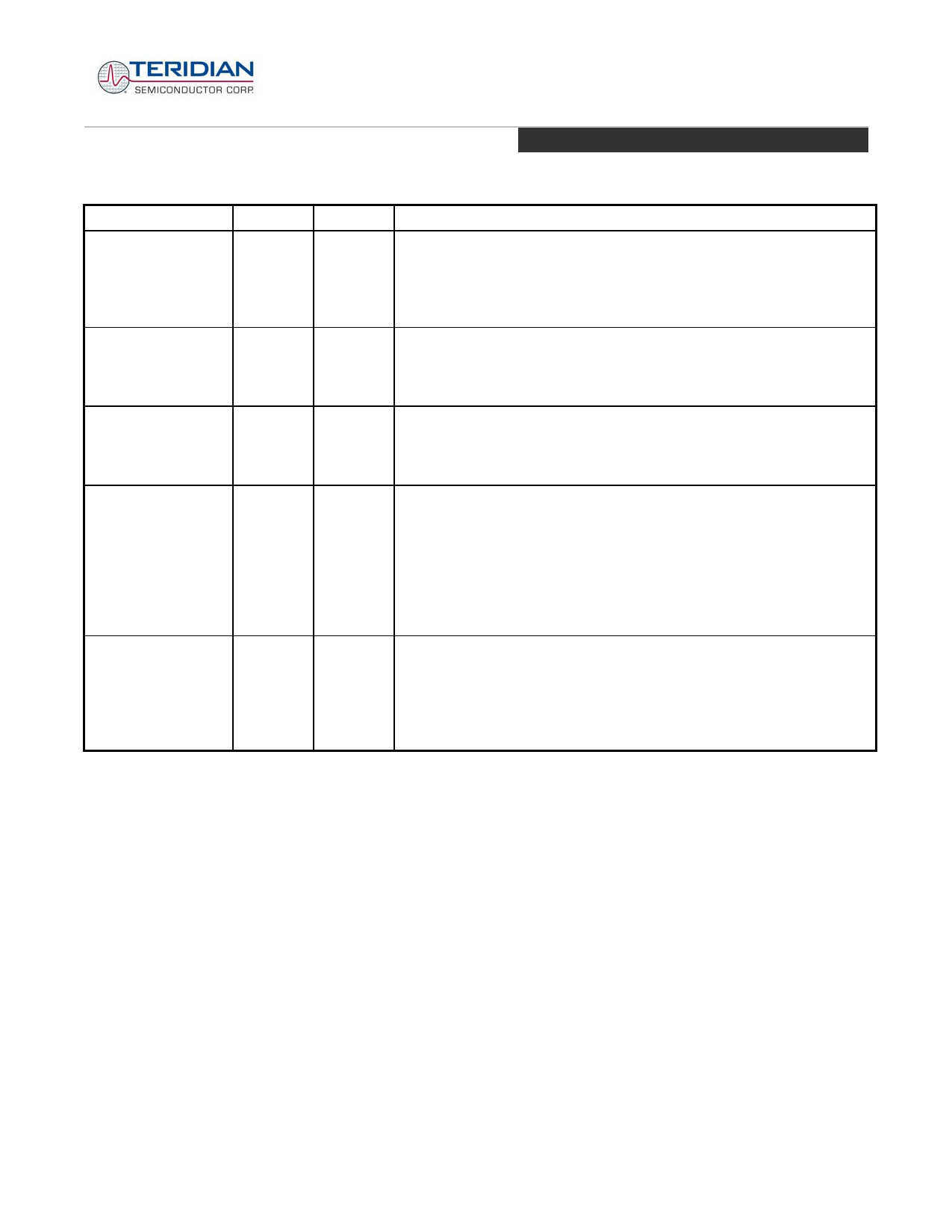

DTE USER

NAME

EXCLK

RXCLK

RXD

TXCLK

TXD

.

73K224BL

V.22bis, V.22, V.21, Bell 212A, 103

Single-Chip Modem w/ Integrated Hybrid

DATA SHEET

PIN

TYPE DESCRIPTION

22

I

EXTERNAL CLOCK: This signal is used in synchronous

transmission when the external timing option has been selected.

In the external timing mode the rising edge of EXCLK is used to

strobe synchronous DPSK transmit data applied to on the TXD

pin. Also used for serial control interface.

26

O

RECEIVE CLOCK: The falling edge of this clock output is

coincident with the transitions in the serial received data output.

The rising edge of RXCLK can be used to latch the valid output

data. RXCLK will be valid as long as a carrier is present.

25

O

RECEIVED DATA OUTPUT: Serial receive data is available on

this pin. The data is always valid on the rising edge of RXCLK

when in synchronous mode. RXD will output constant marks if no

carrier is detected.

21

O

TRANSMIT CLOCK: This signal is used in synchronous

transmission to latch serial input data on the TXD pin. Data must

be provided so that valid data is available on the rising edge of

the TXCLK. The transmit clock is derived from different sources

depending upon the synchronization mode selection. In internal

mode the clock is generated internally. In external mode TXCLK

is phase locked to the EXCLK pin. In slave mode TXCLK is

phase locked to the RXCLK pin. TXCLK is always active.

24

I

TRANSMIT DATA INPUT: Serial data for transmission is applied

on this pin. In synchronous modes, the data must be valid on the

rising edge of the TXCLK clock. In asynchronous modes

(1200/600 bit/s or 300 baud) no clocking is necessary. DPSK

data must be 1200/600 bit/s +1%, -2.5% or +2.3%, -2.5 % in

extended over speed mode.

Page: 7 of 33

© 2005, 2008 TERIDIAN Semiconductor Corporation

Rev 7.1