AD5241BRUZ100 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

生产厂家

AD5241BRUZ100 Datasheet PDF : 20 Pages

| |||

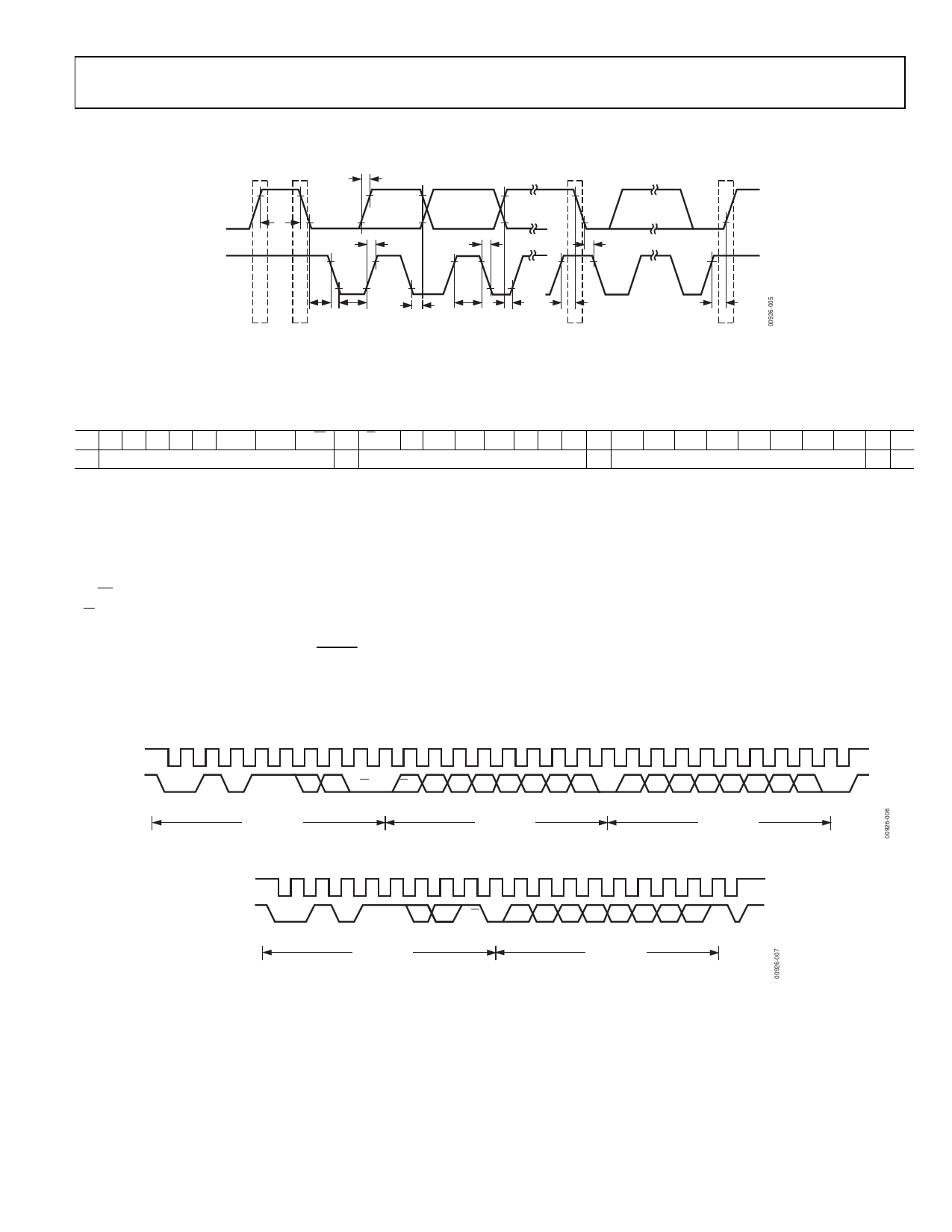

TIMING DIAGRAMS

AD5241/AD5242

t8

SDA

t1

t8

t9

t2

SCL

t2

P

S

t3

t4

t6

t7

t5

S

Figure 3. Detail Timing Diagram

t10

P

Data of AD5241/AD5242 is accepted from the I2C bus in the following serial format.

Table 2.

S 0 1 0 1 1 AD1 AD0 R/W A A/B

Slave Address Byte

RS SD O1 O2 X X X A D7 D6 D5 D4 D3 D2 D1 D0 A P

Instruction Byte

Data Byte

where:

S = start condition

P = stop condition

A = acknowledge

X = don’t care

AD1, AD0 = Package pin programmable address bits. Must be matched with the logic states at Pins AD1 and AD0.

R/W = Read enable at high and output to SDA. Write enable at low.

A/B = RDAC subaddress select; 0 for RDAC1 and 1 for RDAC2.

RS = Midscale reset, active high.

SD = Shutdown in active high. Same as SHDN except inverse logic.

O1, O2 = Output logic pin latched values

D7, D6, D5, D4, D3, D2, D1, D0 = data bits.

SCL

SDA

START BY

MASTER

1

91

91

9

0 1 0 1 1 AD1 AD0 R/W

A/B RS SD O1 O2 X X X

D7 D6 D5 D4 D3 D2 D1 D0

FRAME 1

SLAVE ADDRESS BYTE

ACK BY

AD5241

FRAME 2

INSTRUCTION BYTE

ACK BY

AD5241

FRAME 3

DATA BYTE

ACK BY

AD5241

STOP BY

MASTER

Figure 4. Writing to the RDAC Serial Register

1

91

9

SCL

SDA

START BY

MASTER

0 1 0 1 1 AD1 AD0 R/W

D7 D6 D5 D4 D3 D2 D1 D0

FRAME 1

SLAVE ADDRESS BYTE

ACK BY

NO ACK BY

AD5241

MASTER

FRAME 2

DATA BYTE FROM PREVIOUSLY SELECTED

STOP BY

MASTER

RDAC REGISTER IN WRITE MODE

Figure 5. Reading Data from a Previously Selected RDAC Register in Write Mode

Rev. C | Page 5 of 20