AD7992(RevPrH) 查看數據表(PDF) - Analog Devices

零件编号

产品描述 (功能)

生产厂家

AD7992

(Rev.:RevPrH)

(Rev.:RevPrH)

AD7992 Datasheet PDF : 21 Pages

| |||

AD7992

PRELIMINARY TECHNICAL DATA

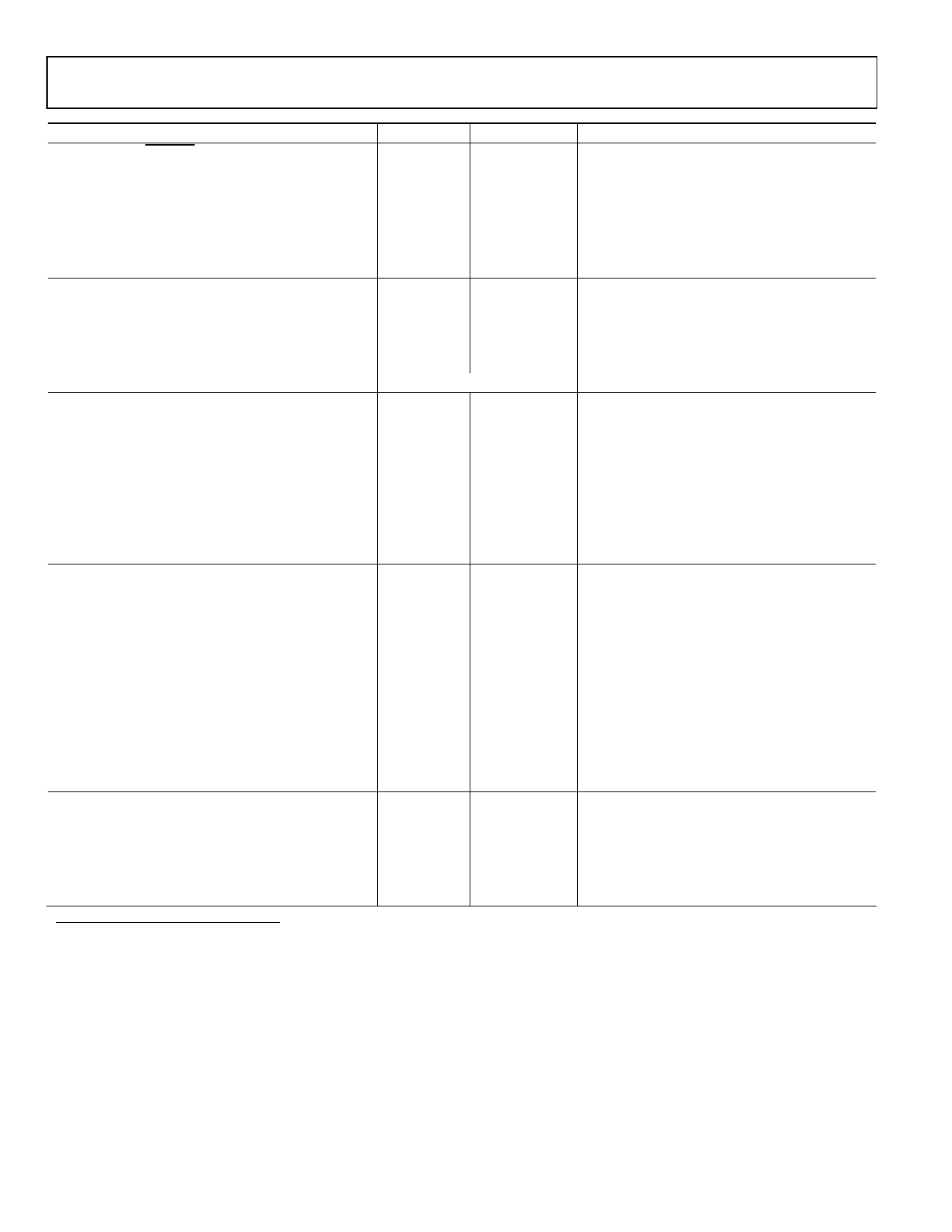

I2C TIMING SPECIFICATIONS1 (Continued.)

AD7992

Parameter Conditions

Limit at TMIN, TMAX

MIN

MAX Unit

t4

Standard Mode

Fast Mode

0

3.45 µs

0

0.9 µs

High-Speed Mode, CB = 100pF max 0

70

ns

High-Speed Mode, CB = 400pF max 0

150 ns

t5

Standard Mode

4.7

µs

Fast Mode

0.6

µs

High-Speed Mode

t6

Standard Mode

Fast Mode

160

ns

4

µs

0.6

µs

High-Speed Mode

t7

Standard Mode

Fast Mode

t8

Standard Mode

Fast Mode

160

ns

4.7

µs

1.3

µs

4

µs

0.6

µs

High-Speed Mode

160

ns

t9

Standard Mode

-

1000 ns

Fast Mode

20 + 0.1CB 300 ns

High-Speed Mode, CB = 100pF max 10

80

ns

High-Speed Mode, CB = 400pF max 20

160 ns

t10

Standard Mode

-

300 ns

Fast Mode

20 + 0.1CB 300 ns

High-Speed Mode, CB = 100pF max 10

80

ns

High-Speed Mode, CB = 400pF max 20

160 ns

t11

Standard Mode

-

1000 ns

Fast Mode

20 + 0.1CB 300 ns

High-Speed Mode, CB = 100pF max 10

40

ns

High-Speed Mode, CB = 400pF max 20

80

ns

t11A

Standard Mode

-

1000 ns

Fast Mode

20 + 0.1CB 300 ns

High-Speed Mode, CB = 100pF max 10

80

ns

High-Speed Mode, CB = 400pF max 20

160 ns

t12

Standard Mode

-

300 ns

Fast Mode

20 + 0.1CB 300 ns

High-Speed Mode, CB = 100pF max 10

40

ns

High-Speed Mode, CB = 400pF max 20

t

S

4

P

Fast Mode

0

80

ns

50

ns

High-Speed Mode

0

10

ns

tPOWER-UP

1

µs

Description

tHD;DAT, Data Hold Time

tSU;STA, Set-up Time for a repeated START

Condition

tHD;STA, Hold Time (repeated) START

Condition

tBUF, Bus Free Time Between a STOP and a

START Condition.

tSU;STO, Set-up Time for STOP Condition

tRDA, Rise time of SDA signal

tFDA, Fall time of SDA signal

tRCL, Rise time of SCL signal

tRCL1, Rise time of SCL signal after a re-

peated START Condition and after an

Acknowledge bit.

tFCL, Fall Time of SCL signal

Pulsewidth of Spike Suppressed.

Power-up Time

NOTES

1See Figure 1. Hs-Mode timing specification apply to the AD7992-1 only, Standard, Fast Mode Timing specifications apply to both the

AD7992-0 and AD7992-1. CB refers tothe capacitance load on the bus line.

2The SDA and SCL timing is measured with the input filters enabled. Switching off the input filters improves the transfer rate but has a nega-

tive effect on EMC behavior of the part.

4Input filtering on both the SCL and SDA inputs suppress noise spikes that are less than 50ns or 10ns for Fast Mode or High-Speed mode

respectivley.

Specifications subject to change without notice.

–4–

REV. PrH