AHA4013B-050PJC 查看數據表(PDF) - Unspecified

零件编号

产品描述 (功能)

生产厂家

AHA4013B-050PJC Datasheet PDF : 28 Pages

| |||

Advanced Hardware Architectures, Inc.

The use of internal buffers is restricted per the

rules defined in Section 2.9 Data Rates and

Latencies.

Maximum delay required for each block of a

given length to pass through the device is fixed, and

does not vary with the location or the number of

errors received. This delay (or latency), expressed

in the number of clocks is discussed in a later

section.

2.2 CORRECTING CAPABILITY AND

POLYNOMIALS

Compared with other codes, RS codes require

relatively few “overhead” check bytes to be added

to the data stream to achieve a high degree of error

detection and correction. Since the AHA4013B

deals with bytes (or symbols) rather than with

individual bits, when a byte is in error it does not

matter how many bits within the byte are corrupted;

it is counted as one error.

The Reed-Solomon code is defined over the

finite field GF(28). The field defining primitive

polynomial is:

P(x) = x8 + x7 + x2 + x + 1

and the generator polynomial, dependent on the

variable R, is given by:

119 + R

∏ G(x) =

(x – αi)

i = 120

where R ∈ {2, 3, 4, 5,... 20} for the AHA4013B. This

polynomial is specified in international standards,

Intelsat IESS 308; RTCA DO-217 Appendix F (Rev

D) and the proposed CCITT SG-18.

For every 2 check bytes, the decoder corrects

either 2 erasures or 1 error. An erasure can be

determined with a parity detector or a signal dropout

detector external to the chip. An erasure is indicated

by the ERASE signal when the erased byte is

clocked in the device.

Correcting “erasures” takes only half as much

of the correction capability of the RS code as it takes

to correct “errors”, since the position information is

already known for “erasures”. The correction ability

of the code is bounded as:

R ≥ # erasures + 2(# errors)

Valid block length (N) is defined by the

relationship:

R + 1 ≤ N ≤ 255

where R ranges from 2 to 20.

A complete codeword can therefore range from

a minimum of 3 bytes to a maximum of 255 bytes.

For further discussion on error rate

performance, refer to Section 2.10 Reed-Solomon

(ECC) Module and Error Rate Performance.

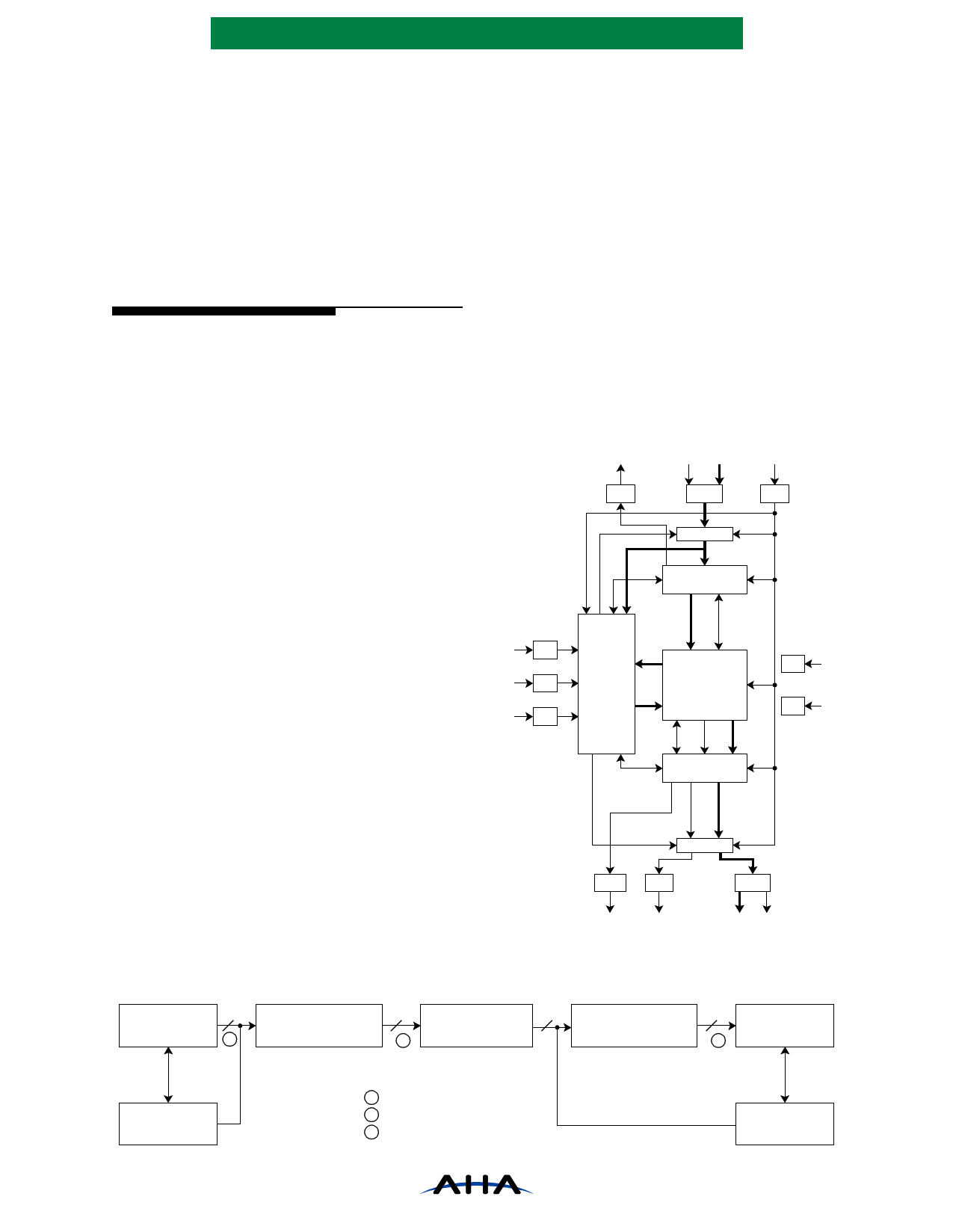

Figure 1: Block Diagram

RDYIN

ERASE DI[7:0]

CLK

RDYIN

DI

CLK

REGISTER

INPUT BUFFER

367x9

RSTN RSTN

DSIN DSIN

DSON DSON

CONTROL

ECC CORE

OUTPUT BUFFER

256x9

GND GND

VDD VDD

REGISTER

RDYON

CRTN

RDYON

CRTN

DO

DO[7:0] ERR

Figure 2: Typical Applications Diagram

ENCODER

COMMUNICATIONS

DECODER

DATA SOURCE 8

A

AHA4013B

ECC COPROCESSOR

8

B

CHANNEL

1 TO x BITS WIDE

8

AHA4013B

8

ECC COPROCESSOR C

DATA SINK

SYSTEM

CONTROLLER

BLOCK FORMAT AT:

A KDATA PLUS R “DUMMY” BYTES

B KDATA PLUS R CHECK BYTES

C KDATA BYTES

SYSTEM

CONTROLLER

PS4013B-0600

Page 3 of 24