NT512D64S8HA0G-75B 查看數據表(PDF) - Nanya Technology

零件编号

产品描述 (功能)

生产厂家

NT512D64S8HA0G-75B Datasheet PDF : 14 Pages

| |||

NT512D64S8HAAG

512MB : 64M x 64

PC2100 / PC1600 Unbuffered DIMM

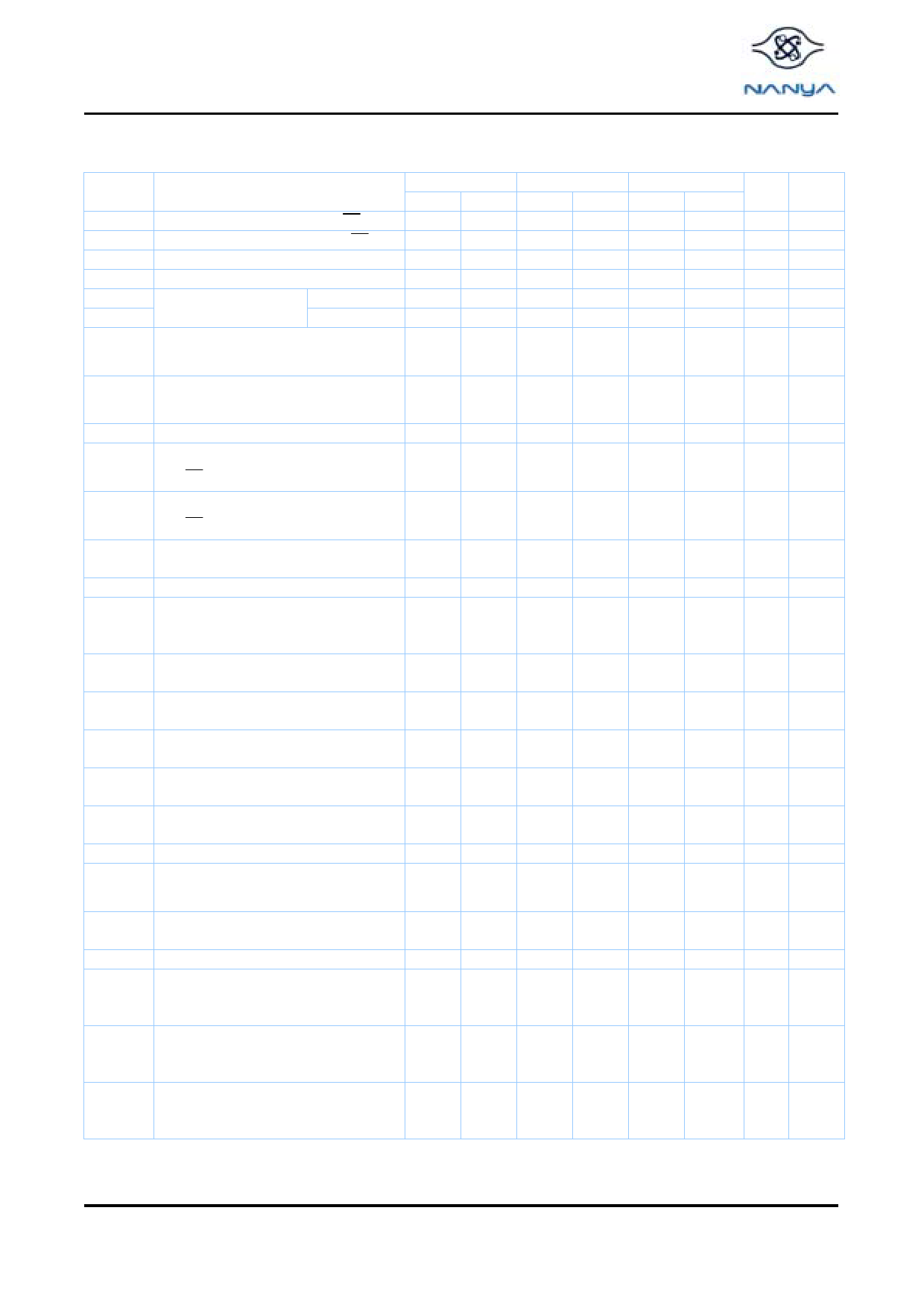

AC Timing Specifications for DDR SDRAM Devices Used on Module

(TA = 0 °C ~ 70 °C; VDDQ = 2.5V ± 0.2V; VDD = 2.5V ± 0.2V, See AC Characteristics) (Part 1 of 2)

Symbol

tAC

tDQSCK

tCH

tCL

tCK

tCK

Parameter

DQ output access time from CK/ CK

DQS output access time from CK/ CK

CK high-level width

CK low-level width

Clock cycle time

CL=2.5

CL=2

-7K

Min. Max.

-0.75 +0.75

-0.75 +0.75

0.45 0.55

0.45 0.55

7

12

7.5

12

-75B

Min. Max.

-0.75 +0.75

-0.75 +0.75

0.45 0.55

0.45 0.55

7.5

12

10

12

-8B

Min.

Max.

-0.8

+0.8

-0.8

+0.8

0.45

0.55

0.45

0.55

8

12

10

12

tDH

DQ and DM input hold time

0.5

0.5

0.6

tDS

DQ and DM input setup time

0.5

0.5

0.6

tDIPW

tHZ

tLZ

tDQSQ

tDQSQA

tHP

tQH

tDQSS

tDQSL,H

tDSS

tDSH

tMRD

DQ and DM input pulse width (each input)

Data-out high-impedance time from

CK/ CK

1.75

-0.75

+0.75

1.75

-0.75

+0.75

Data-out low-impedance time from

CK/ CK

DQS-DQ skew (DQS & associated DQ

signals)

DQS-DQ skew (DQS & all DQ signals)

Minimum half clk period for any given

cycle; defined by clk high(tCH )

or clk low (tCL ) time

Data output hold time from DQS

Write command to 1st DQS latching

transition

DQS input low (high) pulse width

(write cycle)

DQS falling edge to CK setup time

(write cycle)

DQS falling edge hold time from CK

(write cycle)

Mode register set command cycle time

-0.75 +0.75 -0.75 +0.75

tCH

or

tCL

tHP -

0.75ns

0.75

0.5

0.5

1.25

tCH

or

tCL

tHP -

0.75ns

0.75

0.5

0.5

1.25

0.35

0.35

0.2

0.2

0.2

0.2

14

15

2

-0.8

-0.8

tCH

or

tCL

tHP -

1.0ns

0.75

0.35

0.2

0.2

16

tWPRES Write preamble setup time

0

0

0

+0.8

+0.8

0.6

0.6

1.25

tWPST

tWPRE

tIH

Write postamble

Write preamble

Address and control input hold time

(fast slew rate)

Address and control input setup time

tIS

(fast slew rate)

Address and control input hold time

tIH

(slow slew rate)

0.40

0.60

0.40

0.60

0.40

0.60

0.25

0.25

0.25

0.9

1.1

1.1

0.9

1.1

1.1

1.0

1.1

1.1

Unit Notes

ns 1,2,3,4

ns 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

ns 1,2,3,4

ns 1,2,3,4

1,2,3,4

ns

,15,16

1,2,3,4

ns

,15,16

ns 1,2,3,4

1, 2, 3,

ns

4, 5

1, 2, 3,

ns

4, 5

ns 1,2,3,4

ns 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

tCK 1,2,3,4

ns 1,2,3,4

1, 2, 3,

ns

4, 7

1, 2, 3,

tCK

4, 6

tCK 1,2,3,4

2, 3, 4,

ns 9, 11,

12

2, 3, 4,

ns 9, 11,

12

2, 3, 4,

ns 10, 11,

12, 14

REV 1.0 06 / 2002

11

© NANYA TECHNOLOGY CORP.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.