ARM28XXT 查看數據表(PDF) - International Rectifier

零件编号

产品描述 (功能)

生产厂家

ARM28XXT Datasheet PDF : 13 Pages

| |||

ARM28XXT Series

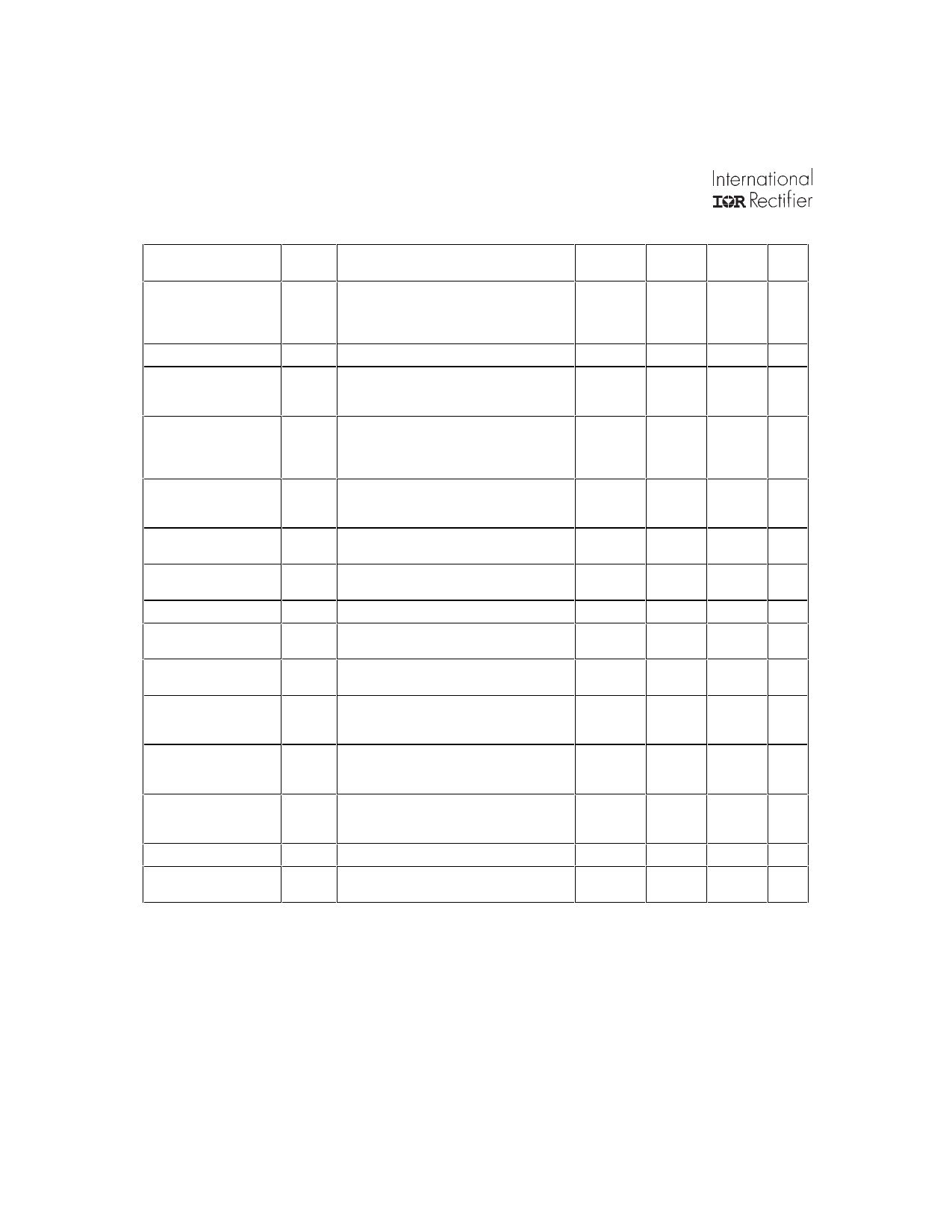

Group A Tests VIN= 28Volts, CL =0 unless otherwise specified.

Test

Symbol Conditions unless otherwise specified

Output voltage accuracy

VOUT

IOUT = 1.5 Adc

IOUT = ±250mAdc

IOUT = ±250mAdc

(main)

ARM2812(dual)

ARM2815(dual)

Output power Note 1

POUT VIN = 19 V, 28V, 50 V

Output current

Note 1

IOUT VIN 19 V, 28V, 50 V

(main)

(dual)

IOUT = 150, 1500, 3000mAdc

(main)

Output regulation Note 4 VR VIN = 19 V, 28V, 50 V

IOUT = ±75, ±310, ±625mAdc 2812(dual)

IOUT = ±75, ±250, ±500mAdc 2815(dual)

Input current

IOUT = minimum rated, Pin 3 open

IIN

Pin 3 shorted to pin 2 (disabled)

Output ripple Note 2

VRIP VIN = 19 V, 28V, 50 V

IOUT = 3000mA main, ±500mA dual

Input ripple Note 2

IRIP VIN = 19 V, 28V, 50 V

IOUT = 3000mA main, ±500mA dual

Switching frequency

FS Synchronization pin (pin 6) open

Efficiency

Eff IOUT = 800mA main, ±500mA dual

Power dissipation,

load fault

Output response to step

load changes Notes 3, 5

Recovery time from step

load changes Notes 5, 6

Turn on overshoot

Turn on delay Note 7

Isolation

PD Short circuit, any output

10% Load to/from 50% load

VTL

50% Load to/from 100% load

10% Load to/from 50% load

TTL

50% Load to/from 100% load

VOS IOUT = minimum and full rated

(main)

(dual)

TDLY IOUT = minimum and full rated

ISO 500VDC Input to output or any pin to case

(except pin 12)

Group A

Subgroups Min

1, 2, 3

4.95

1, 2, 3

1, 2, 3

1, 2, 3

1, 2, 3

±11.70

±14.50

3.0

150

1, 2, 3

75

1, 2, 3

4.8

1, 2, 3

1, 2, 3

1, 2, 3

±11.1

±14.0

1, 2, 3

1, 2, 3

1, 2, 3

4, 5, 6

225

1

80

2, 3

78

1, 2, 3

4, 5, 6

-200

4, 5, 6

-200

4, 5, 6

4, 5, 6

4, 5, 6

4, 5, 6

4, 5, 6

5.0

1

100

Max

5.05

±12.30

±15.15

30

3000

500

5.2

±12.9

±15.8

250

8.0

100

Units

V

W

mA

V

mA

mVP-P

150

mAP-P

275

KHz

%

7.5

W

200

200

200

200

500

1500

20

mVPK

µs

mV

ms

MΩ

Notes to Group A Test Table

1. Parameter verified during dynamic load regulation tests

2. Guaranteed for DC to 20 MHz bandwidth. Test conducted using a 20KHz to 2MHz bandwidth.

3. Load current is stepped for output under test while other outputs are fixed at half rated load.

4. Each output is measured for all combinations of line and load. Only the minimum and maximum readings for each output are recorded.

5. Load step transition time ≥ 10µS.

6. Recovery time is measured from the initiation of the transient to where V has returned to within ±1% of its steady state value.

OUT

7. Turn on delay time is tested by application of a logical low to high transition on the enable pin (pin 3) with power present at the input.

8. Subgroups 1 and 4 are performed at +25°C, subgroups 2 and 5 at -55°C and subgroups 3 and 6 at +125°C.

4

www.irf.com