AZ100LVEL16VTXP 查看數據表(PDF) - Arizona Microtek, Inc

零件编号

产品描述 (功能)

生产厂家

AZ100LVEL16VTXP Datasheet PDF : 13 Pages

| |||

AZ100LVEL16VT

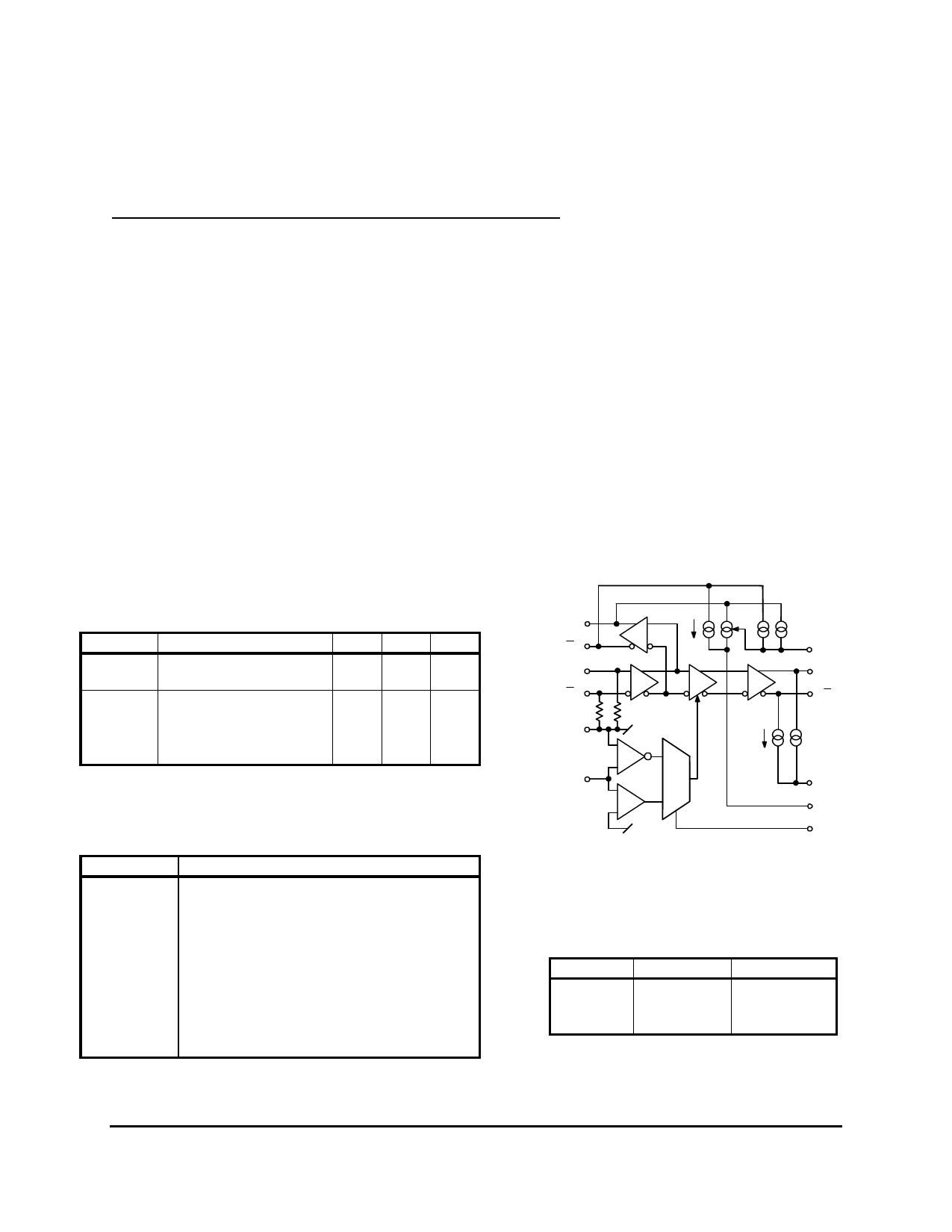

Outputs QHG and Q¯ HG each have an optional on-chip pull-down current source of 10 mA. When pad/pin VEEP is

left open (NC), the output current sources are disabled and the QHG /Q¯ HG operate as standard PECL/ECL. When VEEP

is connected to VEE, the current sources are activated. The QHG /Q¯ HG pull-down current can be decreased, by using a

resistor to connect VEEP to VEE. (See graph on page 5.)

MLP 8, 2x2 mm Package, VTNA, VTNB, VTNC & VTND Versions

All MLP 8, 2x2mm versions of the AZ100LVEL16VT provide an enable input that allows continuous oscillator

operation. VTNA and VTNB utilize an enable (E¯N¯ ) that operates in the PECL/ECL mode. When the E¯N¯ input is

LOW, the Q¯ and QHG/Q¯ HG outputs follow the data inputs. When E¯N¯ is HIGH, the QHG output is forced high and the

Q¯ HG output is forced low. VTNC and VTND utilize an enable (EN) that operates in the CMOS/TTL mode. When the

EN input is HIGH, the Q¯ and QHG/Q¯ HG outputs follow the data inputs. When EN is LOW, the QHG output is forced

high and the Q¯ HG output is forced low.

For VTNA and VTND, both D and D¯ inputs are brought out and tied to the VBB pin through 470 Ω internal bias

resistors. In VTNB and VTNC, the D¯ input is internally tied directly to the VBB pin and the D input is tied to the VBB

pin through a 470 Ω internal bias resistor. Bypassing VBB to ground with a 0.01 μF capacitor is recommended.

All MLP 8, 2x2mm versions (VTNA, VTNB, VTNC & VTND) have the Q, QHG, and Q¯ HG current sources

disabled, while the Q¯ output operates with a 4 mA current source to VEE.

NOTE: Specifications in the ECL/PECL tables are valid when thermal equilibrium is established.

ENABLE TRUTH TABLE

MLP 16 (VTL) or DIE (VTX)

EN-SEL

EN

Q/Q¯ QHG Q¯ HG

NC

PECL Low, VEE or NC Data Data Data

NC

PECL High or VCC

Data High Low

VEE*

CMOS Low or VEE

Data High Low

VEE*

CMOS High or VCC

Data Data Data

VEE*

VEE*

NC, no external pull-up Data High Low

NC, with ≤20kΩ to VCC Data Data Data

*Connections to VCC or VEE must be less than 1Ω.

PIN

D/D¯

Q/Q¯

QHG/Q¯ HG

VBB

EN-SEL

EN/E¯N¯

CS-SEL

VEEP

VEE

VCC

PIN DESCRIPTION

FUNCTION

Data Inputs

Data Outputs

Data Outputs w/High Gain

Reference Voltage Output

Selects Enable Logic

Enable Input

Selects Q and Q¯ Current Source Magnitude

Optional QHG and Q¯ HG Current Sources

Negative Supply

Positive Supply

Q

Q

D

D

470 Ω

VBB

4mA EA.

470 Ω

10mA EA.

EN

CMOS / TTL

THRESHOLD

MLP 16 (VTL) or DIE (VTX)

CS-SEL

QHG

QHG

VEEP

VEE

EN-SEL

CURRENT SOURCE TRUTH TABLE

MLP 16 (VTL) or DIE (VTX)

CS-SEL

Q

Q¯

NC

4mA typ. 4mA typ.

VEE*

VCC*

8mA typ.

0

8mA typ.

4mA typ.

*Connections to VCC or VEE must be less than 1Ω.

April 2007 * REV - 9

www.azmicrotek.com

2