VSC7960W 查看數據表(PDF) - Vitesse Semiconductor

零件编号

产品描述 (功能)

生产厂家

VSC7960W

VSC7960W Datasheet PDF : 22 Pages

| |||

VITESSE

SEMICONDUCTOR CORPORATION

Advance Product Information

VSC7960

3.125Gb/s CML Limiting Amplifier with LOS Detect

and Laser Driver with Automatic Power Control

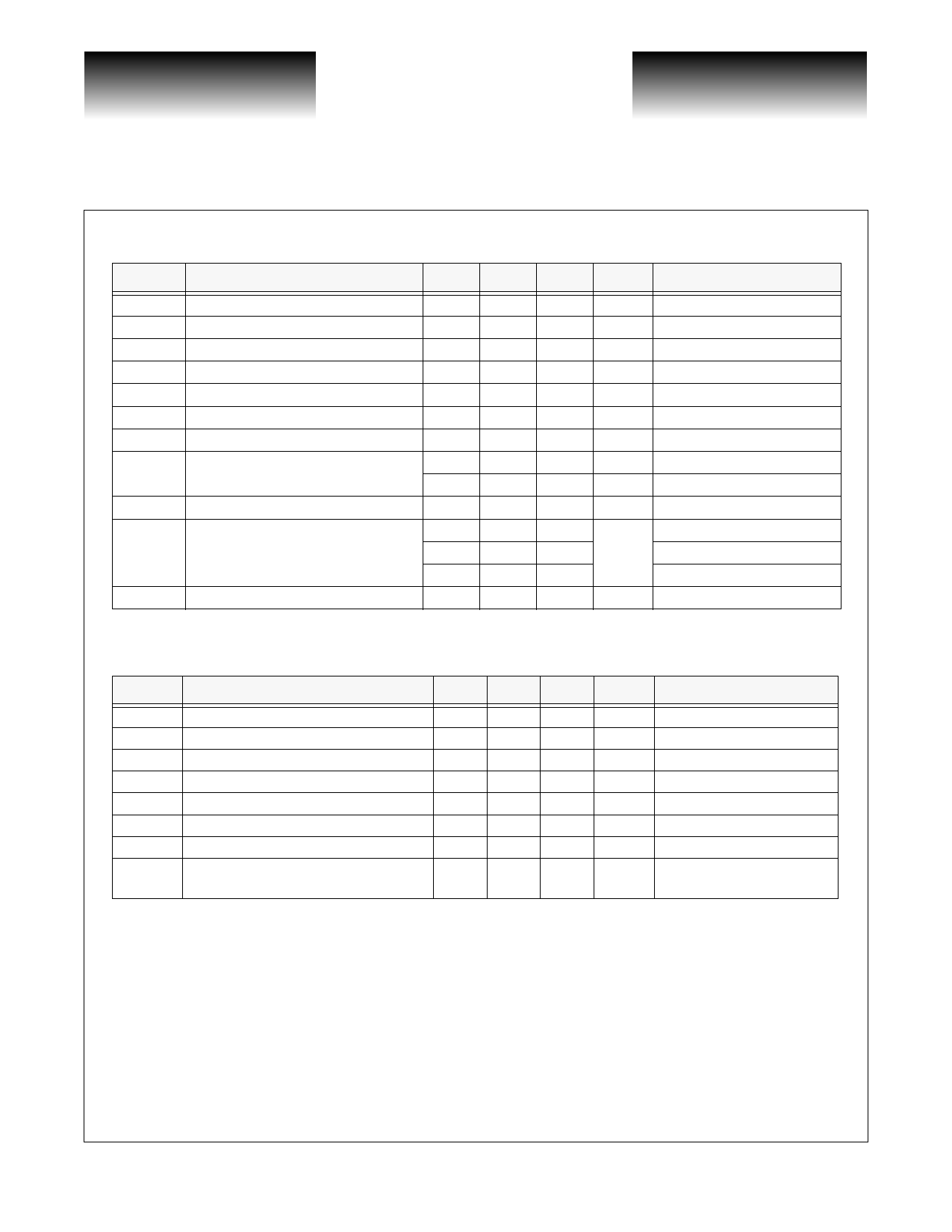

Table 3: Limiting Amplifier AC Specifications

Symbol

Parameter

Min Typ Max Units

Conditions

VIN

JD

JR

tR, tF

vN

RDIFF

fL

VSQ

VCML

ZOUT

Data Rate

Input Voltage Range

Deterministic Jitter

Random Jitter

Rise/Fall Times

Input Referred Noise

Differential Input Resistance

Low Frequency Cut-off

Output Signal when Squelched

CML Output Voltage

Output Resistance

3.125

Gb/s

10

1200 mV peak-to-peak

25

ps See Note 1

8

ps RMS, see Note 2

55

100

ps 20%-80%

230

µV RMS, IN+ to IN-

100

W IN+ to IN-

2

MHz CZ open

2

kHz CZ=0.1µF

20

mV Outputs AC-coupled

550

1100

1200

1800

20

Level=open, RL = 50Ω

mV Level=GND, RL = 75Ω

Squelched

100

Ω Single-ended

NOTES: (1) Deterministic Jitter measured peak-to-peak with K28.5 pattern. (2) Random Jitter measured with minimum input.

Table 4: Laser Driver AC Specifications

Symbol

tSU

tH

tR

tF

PWD

CIDMAX

tJ

Parameter

Input Latch Setup Time

Input Latch Hold Time

Enable/Start-up Delay

Output Rise Time

Output Fall Time

Pulse Width Distortion

Maximum Consecutive Identical Digits

Jitter Generation

Min Typ Max Units

Conditions

100

ps LATCH=high

100

ps LATCH=high

250

ns

60

80

ps 20% to 80%

60

80

ps 20% to 80%

10

50

ps See Notes 1, 2

80

bits

Jitter BW=12kHz to 20MHz,

7

20

psp-p 0-1 pattern.

NOTES: (1) Measured with 622Mb/s 0-1 pattern, LATCH=high. (2) PWD = (wider pulse - narrower pulse) / 2)

G52359-0, Rev 2.1

5/01/01

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

Page 3