DS1706S 查看數據表(PDF) - Dallas Semiconductor -> Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

DS1706S Datasheet PDF : 10 Pages

| |||

DSDS1705/DS1706

DS1705/DS1706

3.3 and 5.0 Volt MicroMonitor

FEATURES

• Halts and restarts an out–of–control microprocessor

• Holds microprocessor in check during power tran-

sients

• Automatically restarts microprocessor after power

failure

• Monitors pushbutton for external override

• Accurate 5%, 10% or 20% resets for 3.3 systems and

5% or 10% resets for 5.0 volt systems

• Eliminates the need for discrete components

• 3.3 volt 20% tolerance for use with 3.0 volt systems

• Pin compatible with the MAXIM MAX705/MAX706 in

8–pin DIP and 8–pin SOIC

• 8–pin DIP, 8–pin SOIC and 8–pin µ–SOP packages

• Industrial temperature range –40°C to +85°C

DESCRIPTION

The DS1705/DS1706 3.3 or 5.0 Volt MicroMonitor moni-

tors three vital conditions for a microprocessor: power

supply, software execution, and external override. A

precision temperature compensated reference and

comparator circuit monitors the status of VCC at the

device and at an upstream point for maximum protec-

tion. When the sense input detects an out–of–tolerance

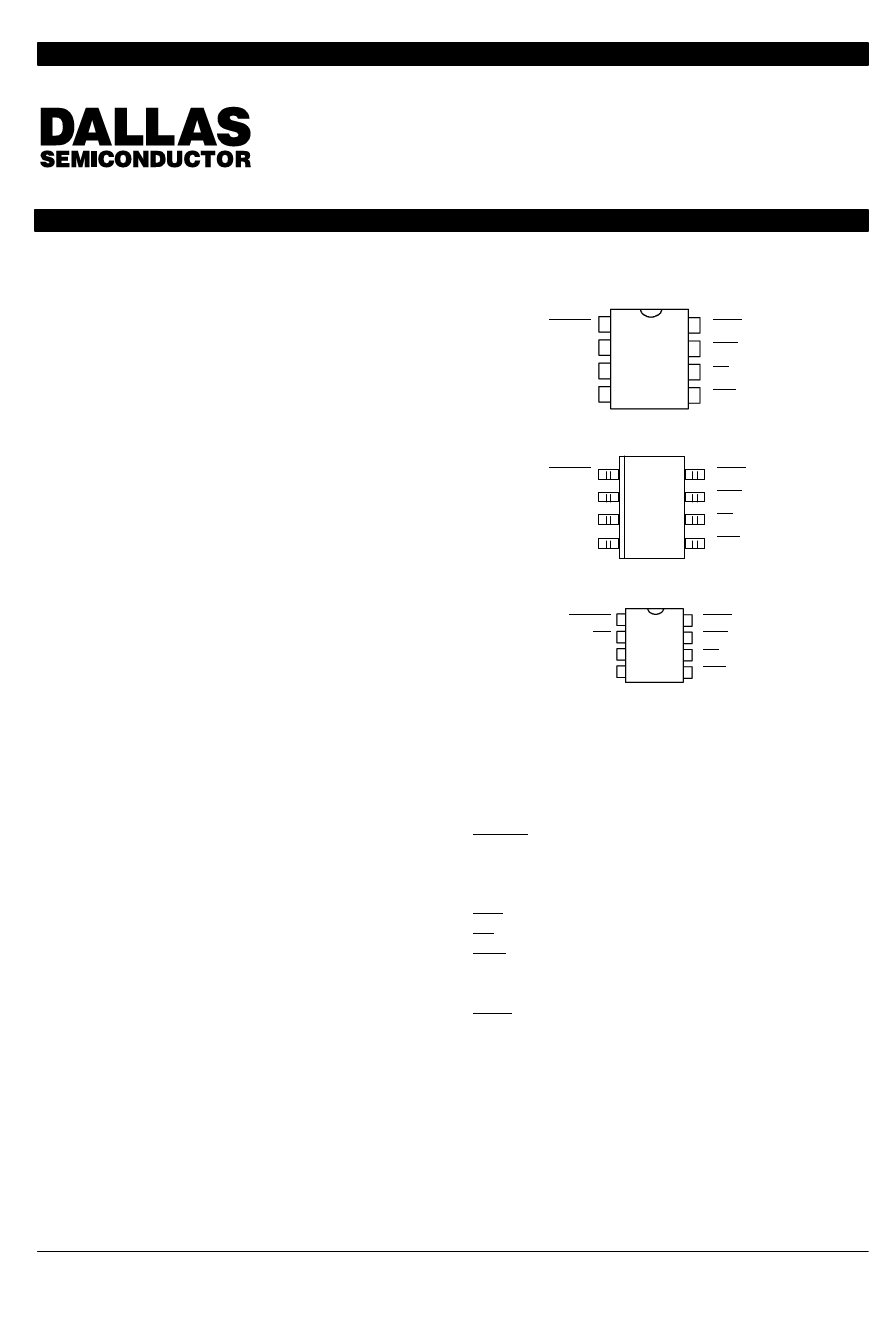

PIN ASSIGNMENT

PBRST

VCC

GND

IN

1

8

2

7

3

6

4

5

8–PIN DIP

(300 MIL)

WDS

RST

ST

NMI

PBRST

VCC

GND

IN

1

8

2

7

3

6

4

5

8–PIN SOIC

(150 MIL)

WDS

RST (*RST)

ST

NMI

PBRST 1

VCC 2

GND 3

IN 4

8 WDS

7 RST (*RST)

6 ST

5 NMI

8–PIN µ–SOP

(118 MIL)

See Mech. Drawings

Section

DS1705 and DS1706_/R/S/T (*DS1706L and DS1706P)

PIN DESCRIPTION

PBRST

– Pushbutton Reset Input

VCC

GND

– Power Supply

– Ground

IN

– Input

NMI

– Non–maskable Interrupt

ST

– Strobe Input

RST

– Active Low Reset Output

*RST

– Active High Reset Output

(DS1706P and DS1706L only)

WDS

– Watchdog Status Output

condition a non–maskable interrupt is generated. As

the voltage at the device degrades an internal power fail

signal is generated which forces the reset to an active

state. When VCC returns to an in–tolerance condition,

the reset signal is kept in the active state for a minimum

of 130 ms to allow the power supply and processor to

stabilize.

ECopyright 1995 by Dallas Semiconductor Corporation.

All Rights Reserved. For important information regarding

patents and other intellectual property rights, please refer to

Dallas Semiconductor data books.

011296 1/10