AS4LC1M16S1-10TC жҹҘзңӢж•ёж“ҡиЎЁпјҲPDFпјү - Alliance Semiconductor

йӣ¶д»¶зј–еҸ·

дә§е“ҒжҸҸиҝ° (еҠҹиғҪ)

з”ҹдә§еҺӮ家

AS4LC1M16S1-10TC Datasheet PDF : 28 Pages

| |||

AS4LC2M8S1

AS4LC1M16S1

18 A proper power-up initialization sequence (as described on page 10) is needed before proper device operation is ensured. (VDD and VDDQ must be

powered up simultaneously. VSS and VSSQ must be at the same potential.)Two AUTOREFRESH command wake-ups should be repeated any time the tREF

refresh requirement is exceeded.

19 AC characteristics assume tT = 1 ns.

20 In addition to meeting the transition rate specification, the clock and CKE must transit between V IH and VIL (or between VIL and VIH) in a monotonic

manner.

21 Outputs measured at 1.4 V with equivalent load.

Q

30 pF

22 AC timing and IDD tests have VIL = 0V and VIH = 2.8 V with timing referenced to 1.4V crossover point.

23 IDD specifications are tested after the device is properly initialized.

24 Minimum clock cycles = (minimum time/clock cycle time) rounded up.

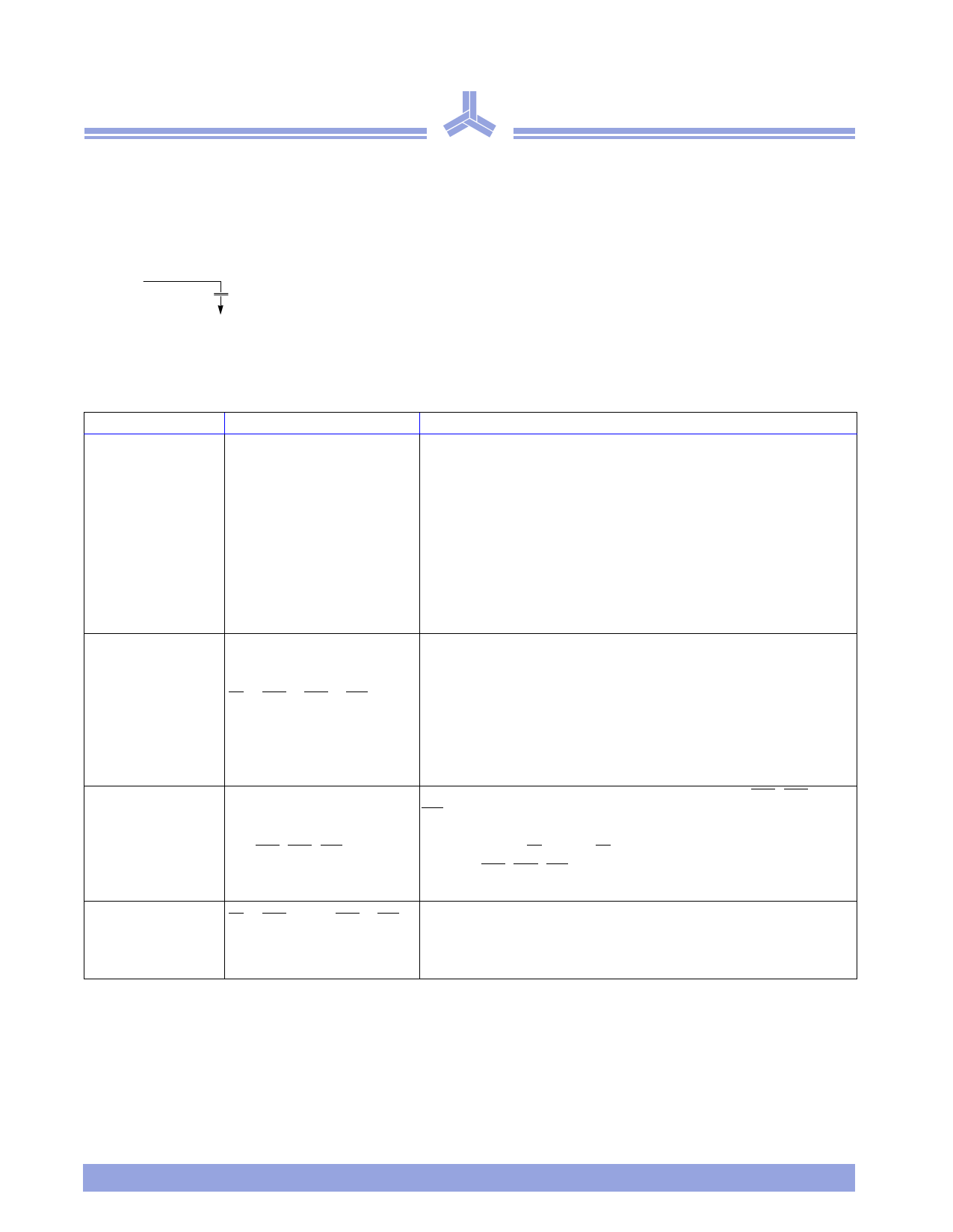

Device operation

Command

Power up

Mode register set

Device deselect and

no operation

Bank activation

Pin settings

Description

The following sequence is recommended prior to normal operation.

1 Apply power, start clock, and assert CKE and DQM high. All other

signals are NOP.

2 After power-up, pause for a minimum of 200Вөs. CKE/DQM =

high; all others NOP.

3 Precharge both banks.

4 Perform Mode Register Set command to initialize mode register.

5 Perform a minimum of 8 auto refresh cycles to stabilize internal

circuitry.

(Steps 4 and 5 may be interchanged.)

The mode register stores the user selected opcode for the SDRAM

operating modes. The CAS latency, burst length, burst type, test mode

and other vendor specific functions are selected/programmed during

CS = RAS = CAS = WE = low; the Mode Register Set command cycle. The default setting of the mode

A0~A11 = opcode

register is not defined after power-up. Therefore, it is recommended

that the power-up and mode register set cycle be executed prior to

normal SDRAM operation. Refer to the Mode Register Set table and

timing for details.

The SDRAM performs a вҖңno operationвҖқ (NOP) when RAS, CAS, and

CS = high, or

RAS, CAS, WE = high

WE = high. Since the NOP performs no operation, it may be used as a

wait state in performing normal SDRAM functions. The SDRAM is

deselected when CS is high. CS high disables the command decoder

such that RAS, CAS, WE and address inputs are ignored. Device

deselection is also considered a NOP.

CS = RAS = low; CAS = WE =

high; A0~A10 = row address;

A11 = bank select

The SDRAM is configured with two internal banks. Use the Bank

Activate command to select a row in one of the two idle banks. Initiate

a read or write operation after tRCD(min) from the time of bank

activation.

10

ALLIANCE SEMICONDUCTOR

7/5/00