CDB43L43 查看數據表(PDF) - Cirrus Logic

零件编号

产品描述 (功能)

生产厂家

CDB43L43 Datasheet PDF : 36 Pages

| |||

CS43L43

3.3.2 Control Port Mode

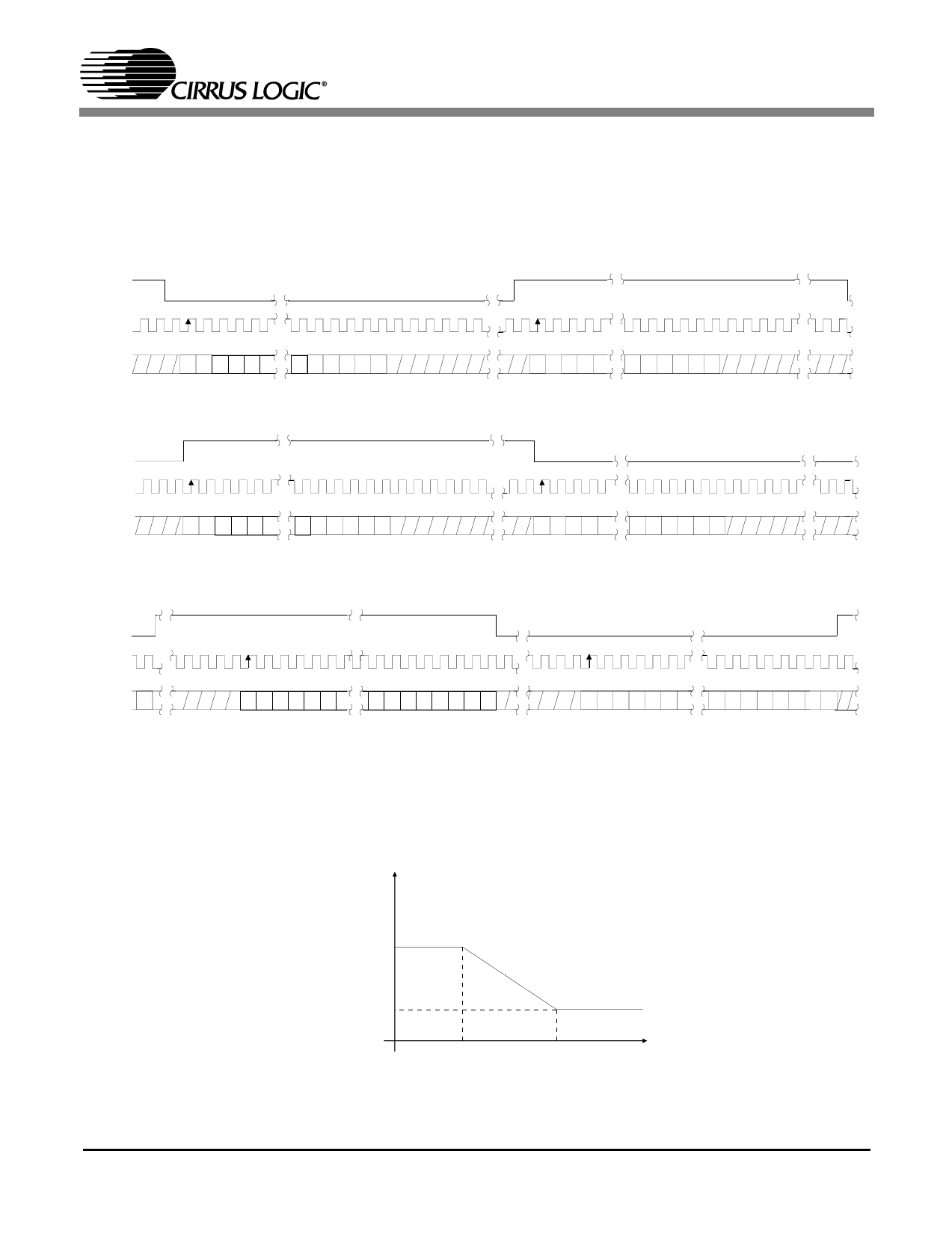

The desired format is selected via the DIF0, DIF1 and DIF2 bits in the Mode Control 2 register (see

section 5.11.2) . For an illustration of the required relationship between LRCK, SCLK and SDATA,

see Figures 2-4.

LRCK

SCLK

SDATA

LRCK

SCLK

SDATA

Left Channel

Right Channel

MSB -1 -2 -3 -4 -5

+5 +4 +3 +2 +1 LSB

MSB -1 -2 -3 -4

Figure 2. I2S Data

+5 +4 +3 +2 +1 LSB

Left Channel

Right Channel

MSB -1 -2 -3 -4 -5

+5 +4 +3 +2 +1 LSB

MSB -1 -2 -3 -4

+5 +4 +3 +2 +1 LSB

Figure 3. Left Justified up to 24-Bit Data

LRCK

SCLK

Left Channel

Right Cha nnel

SDATA MSB

LSB +1 +2 +3 +4 +5

-7 -6 -5 -4 -3 -2 -1 MSB

LSB +1 +2 +3 +4 +5

-7 -6 -5 -4 -3 -2 -1 MSB

32 clo cks

Figure 4. Right Justified Data

3.4 De-Emphasis Control

The device includes on-chip digital de-emphasis. Figure 5 shows the de-emphasis curve for Fs equal to

44.1 kHz. The frequency response of the de-emphasis curve will scale proportionally with changes in sam-

ple rate, Fs. De-emphasis is not available in double-speed mode.

Gain

dB

T1=50 µs

0dB

-10dB

T2 = 15 µs

F1

3.183 kHz

F2 Frequency

10.61 kHz

Figure 5. De-Emphasis Curve

8

DS479PP3