CDB43L43 查看數據表(PDF) - Cirrus Logic

零件编号

产品描述 (功能)

生产厂家

CDB43L43 Datasheet PDF : 36 Pages

| |||

CS43L43

3.4.1 Stand-Alone Mode

When using Internal Serial Clock (see section 3.2.1), pin 3 is available for de-emphasis control and

selects the 44.1 kHz de-emphasis filter. Please see Table 6 for the desired de-emphasis control.

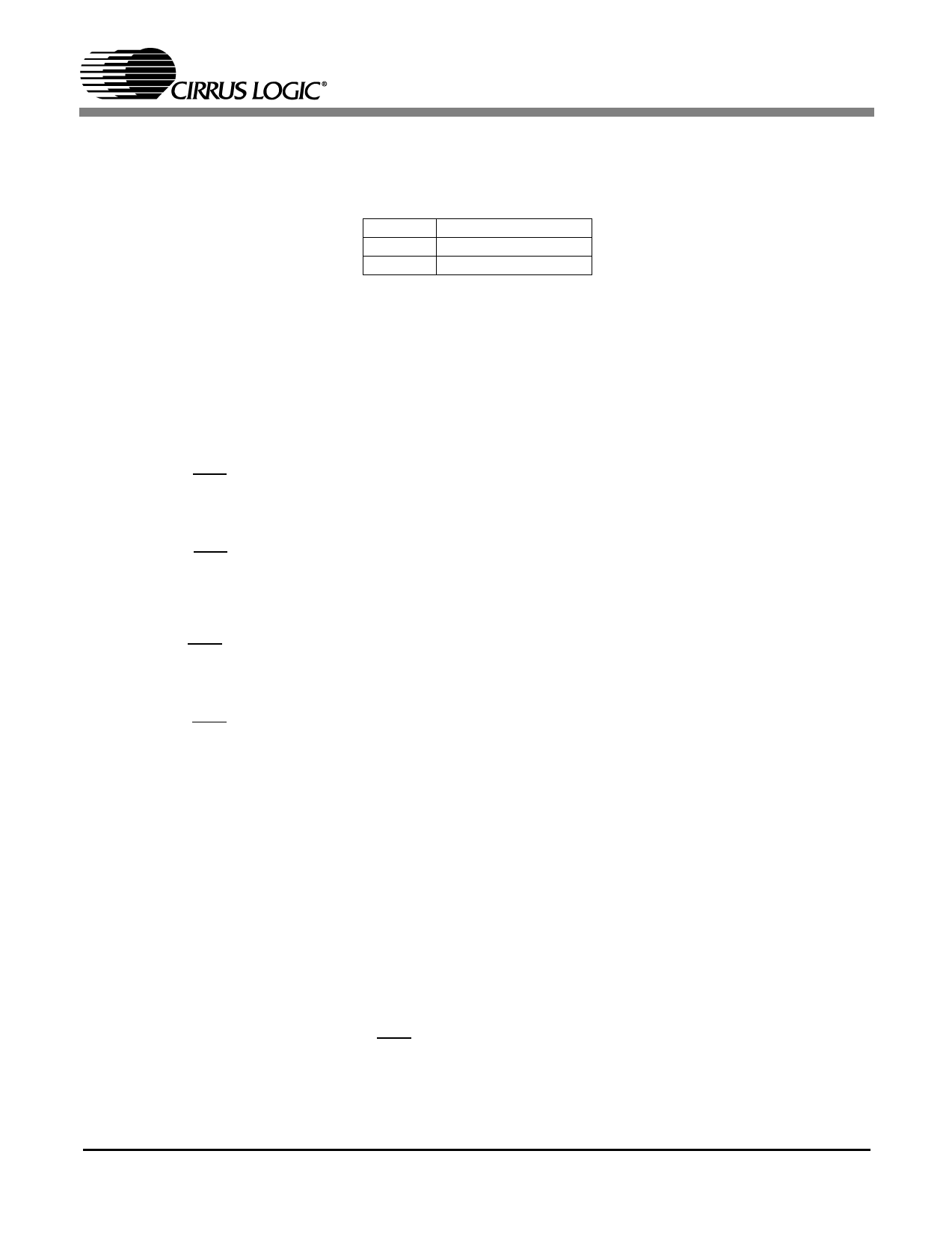

DEM

0

1

DESCRIPTION

Disabled

44.1 kHz

Table 6. De-Emphasis Control

3.4.2 Control Port Mode

The Mode Control bits select either the 32, 44.1, or 48 kHz de-emphasis filter. Please see section

5.7.4 for the desired de-emphasis control.

3.5 Recommended Power-up Sequence

3.5.1 Stand-Alone Mode

1. Hold RST low until the power supply and configuration pins are stable, and the master and

left/right clocks are locked to the appropriate frequences, as discussed in section 3.2. In this state, the

control port is reset to its default settings and VQ_HP will remain low.

2. Bring RST high. The device will remain in a low power state with VQ_HP low and will initiate

the Stand-Alone power-up sequence after approximately 1024 LRCK cycles.

3.5.2 Control Port Mode

1. Hold RST low until the power supply is stable, and the master and left/right clocks are locked to

the appropriate frequences, as discussed in section 3.2. In this state, the control port is reset to its de-

fault settings and VQ_HP will remain low.

2. Bring RST high. The device will remain in a low power state with VQ_HP low. The control port

will be accessible at this time.

3. Wait approximately 2 LRCK cycles and then perform an I2C write to the CP_EN bit prior to the

completion of approximately 1024 LRCK cycles. The desired register settings can be loaded while

keeping the PDN bit set to 1.

4. Set the PDN bit to 0. This will initiate the power-up sequence, which lasts approximately 50 µS

when the POR bit is set to 0. If the POR bit is set to 1, see Section 3.6 for for a complete description

of power-up timing.

3.6 Popguard® Transient Control

The CS43L43 uses Popguard® technology to minimize the effects of output transients during power-up

and power-down. This technology, when used with external DC-blocking capacitors in series with the au-

dio outputs, minimizes the audio transients commonly produced by single-ended single-supply converters.

It is activated inside the DAC when the RST pin is enabled/disabled and requires no other external control,

aside from choosing the appropriate DC-blocking capacitors.

DS479PP3

9