CY7C401 查看數據表(PDF) - Cypress Semiconductor

零件编号

产品描述 (功能)

生产厂家

CY7C401 Datasheet PDF : 13 Pages

| |||

CY7C401/CY7C403

CY7C402/CY7C404

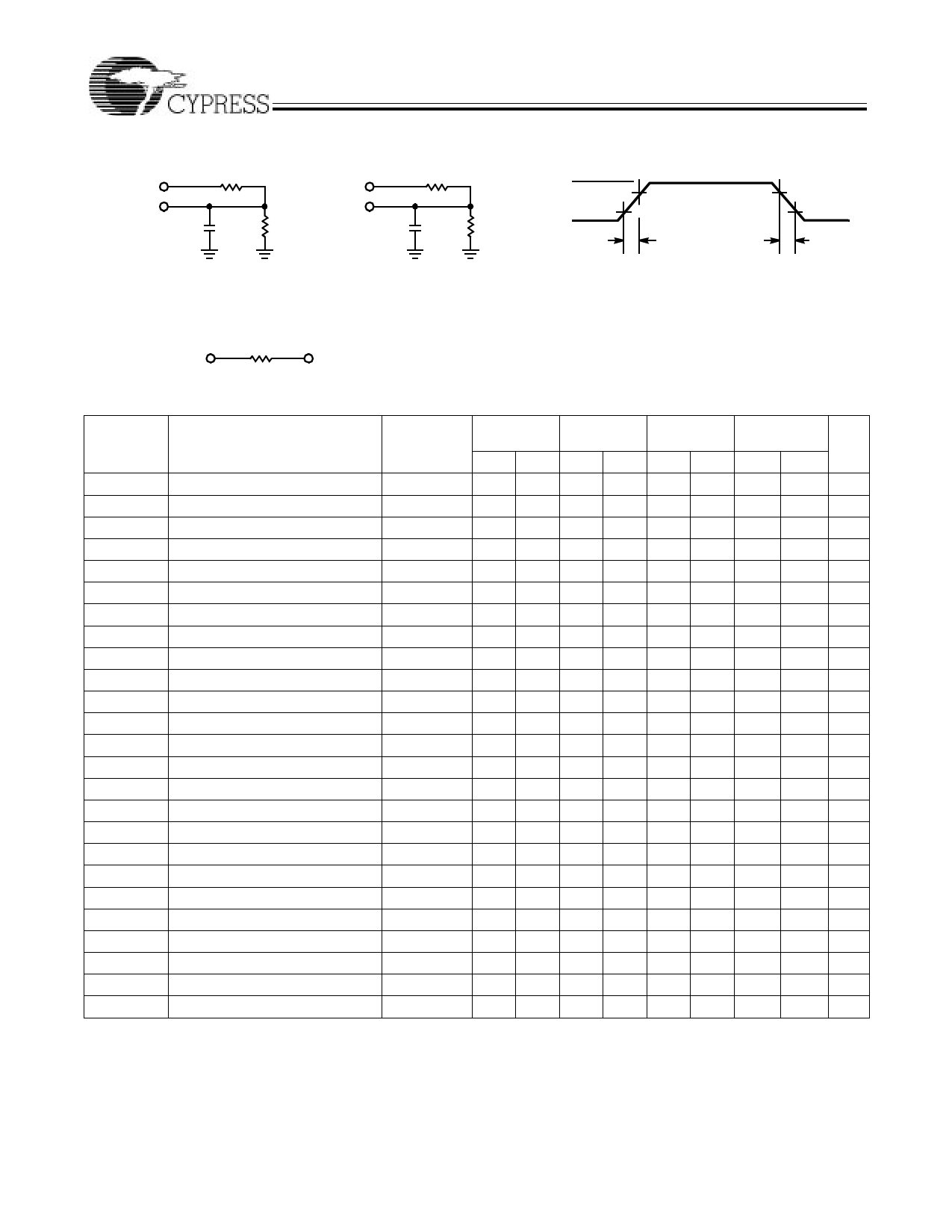

AC Test Loads and Waveforms

R1 437Ω

5V

OUTPUT

30 pF

INCLUDING

JIG AND

SCOPE

(a)

R1 437Ω

5V

OUTPUT

R2

272Ω

5 pF

R2

272Ω

INCLUDING

JIG AND

SCOPE

(b)

C401–6

3.0V

GND

≤ 5 ns

ALL INPUT PULSES

90%

10%

90%

10%

≤ 5 ns

C401–7

Equivalent to: THÉVENIN EQUIVALENT

OUTPUT

167Ω

1.73V

C401–8

Switching Characteristics Over the Operating Range[2, 6]

Parameter

Description

Test

7C401–5

7C402–5 7C40X–10 7C40X–15 7C40X–25[7]

Conditions Min. Max. Min. Max. Min. Max. Min. Max. Unit

fO

Operating Frequency

Note 8

5

10

15

25 MHz

tPHSI

SI HIGH Time

20

20

20

11

ns

tPLSI

SO LOW Time

45

30

25

20

ns

tSSI

Data Set-Up to SI

Note 9

0

0

0

0

ns

tHSI

Data Hold from SI

Note 9

60

40

30

20

ns

tDLIR

Delay, SI HIGH to IR LOW

75

40

35

21/22 ns

tDHIR

Delay, SI LOW to IR HIGH

75

45

40

28/30 ns

tPHSO

SO HIGH Time

20

20

20

11

ns

tPLSO

SO LOW Time

45

25

25

20

ns

tDLOR

Delay, SO HIGH to OR LOW

75

40

35

19/21 ns

tDHOR

Delay, SO LOW to OR HIGH

80

55

40

34/37 ns

tSOR

Data Set-Up to OR HIGH

0

0

0

0

ns

tHSO

Data Hold from SO LOW

5

5

5

5

ns

tBT

Bubble-Through Time

200 10 95 10 65 10 50/60 ns

tSIR

Data Set-Up to IR

Note 10

5

5

5

5

ns

tHIR

Data Hold from IR

Note 10 30

30

30

20

ns

tPIR

Input Ready Pulse HIGH

20

20

20

15

ns

tPOR

Output Ready Pulse HIGH

20

20

20

15

ns

tPMR

MR Pulse Width

40

30

25

25

ns

tDSI

MR HIGH to SI HIGH

40

35

25

10

ns

tDOR

MR LOW to OR LOW

85

40

35

35 ns

tDIR

MR LOW to IR HIGH

85

40

35

35 ns

tLZMR

MR LOW to Output LOW

Note 11

50

40

35

25 ns

tOOE

Output Valid from OE LOW

—

35

30

20 ns

tHZOE

Output High Z from OE HIGH

Note 12

—

30

25

15 ns

Notes:

6. Test conditions assume signal transition time of 5 ns or less, timing reference levels of 1.5V and output loading of the specified IOL/IOH and 30-pF load

capacitance, as in part (a) of AC Test Loads and Waveforms.

7. Commercial/Military

8. I/fO > tPHSI + tDHIR, I/fO > tPHSO + tDHOR

9. tSSI and tHSI apply when memory is not full.

10. tSIR and tHIR apply when memory is full, SI is high and minimum bubble-through (tBT) conditions exist.

11. All data outputs will be at LOW level after reset goes HIGH until data is entered into the FIFO.

12. HIGH-Z transitions are referenced to the steady-state VOH –500 mV and VOL +500 mV levels on the output. tHZOE is tested with 5-pF load capacitance as

in part (b) of AC Test Loads and Waveforms.

3