QL4036-3PB256I 查看數據表(PDF) - QuickLogic Corporation

零件编号

产品描述 (功能)

生产厂家

QL4036-3PB256I

QL4036-3PB256I Datasheet PDF : 12 Pages

| |||

QL4036 - QuickRAMTM

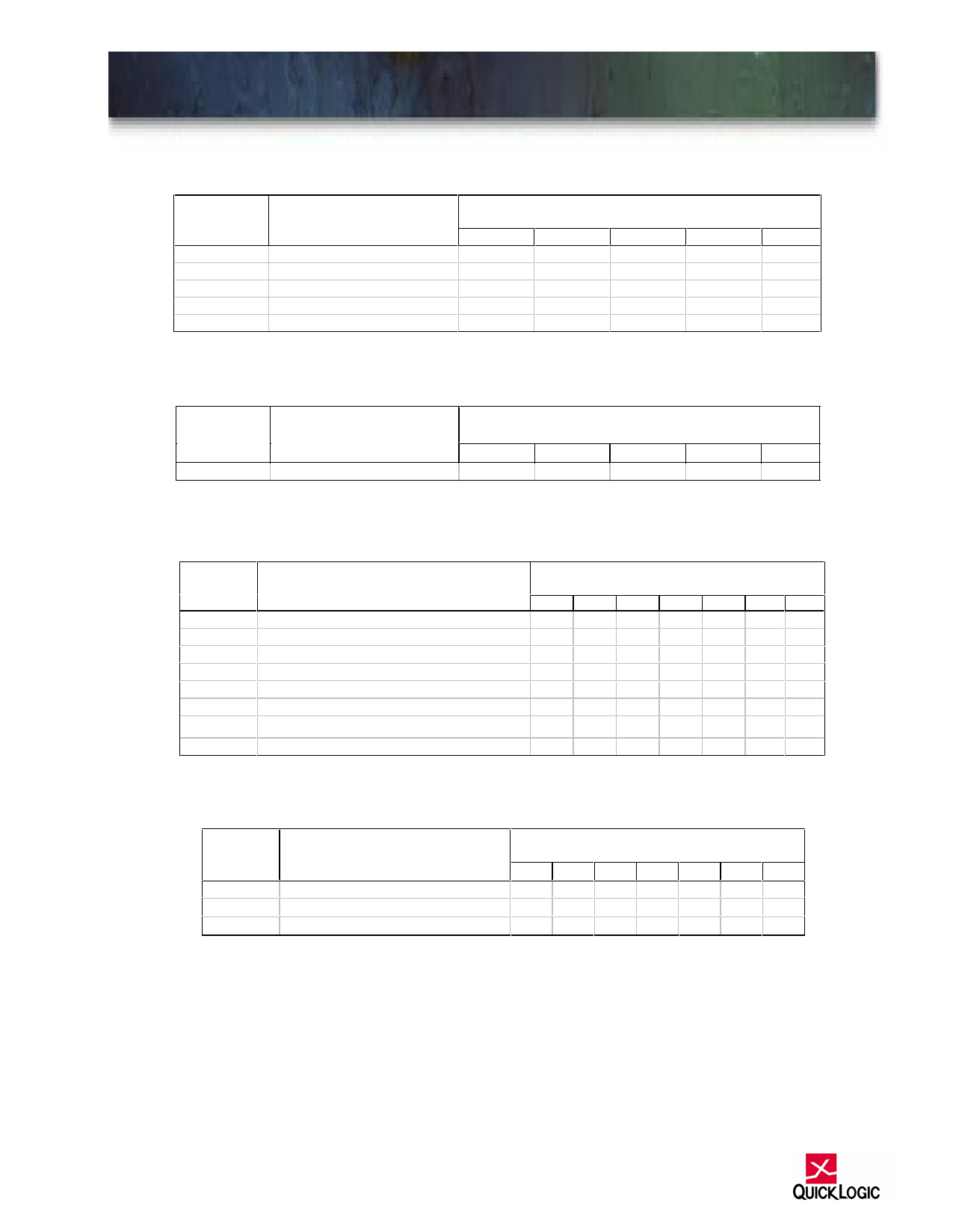

RAM Cell Synchronous Read Timing

Symbol

Parameter

TSRA

THRA

TSRE

THRE

TRCRD

RA Setup Time to RCLK

RA Hold Time to RCLK

RE Setup Time to RCLK

RE Hold Time to RCLK

RCLK to RD [5]

Propagation Delays (ns)

Fanout

1

2

3

4

8

1.0

1.0

1.0

1.0

1.0

0.0

0.0

0.0

0.0

0.0

1.0

1.0

1.0

1.0

1.0

0.0

0.0

0.0

0.0

0.0

4.0

4.3

4.6

4.9

6.1

RAM Cell Asynchronous Read Timing

Symbol

Parameter

RPDRD

RA to RD [5]

Propagation Delays (ns)

Fanout

1

2

3

4

8

3.0

3.3

3.6

3.9

5.1

Symbol

TIN

TINI

TISU

TIH

TlCLK

TlRST

TlESU

TlEH

Input-Only/Clock Cells

Parameter

High Drive Input Delay

High Drive Input, Inverting Delay

Input Register Set-Up Time

Input Register Hold Time

Input Register Clock To Q

Input Register Reset Delay

Input Register Clock Enable Setup Time

Input Register Clock Enable Hold Time

Propagation Delays (ns)

Fanout [5]

1

2

3

4

8 12 24

1.5 1.6 1.8 1.9 2.4 2.9 4.4

1.6 1.7 1.9 2.0 2.5 3.0 4.5

3.1 3.1 3.1 3.1 3.1 3.1 3.1

0.0 0.0 0.0 0.0 0.0 0.0 0.0

0.7 0.8 1.0 1.1 1.6 2.1 3.6

0.6 0.7 0.9 1.0 1.5 2.0 3.5

2.3 2.3 2.3 2.3 2.3 2.3 2.3

0.0 0.0 0.0 0.0 0.0 0.0 0.0

Symbol

tACK

tGCKP

tGCKB

Clock Cells

Parameter

Array Clock Delay

Global Clock Pin Delay

Global Clock Buffer Delay

Propagation Delays (ns)

Loads per Half Column [7]

1 2 3 4 8 10 11

1.2 1.2 1.3 1.3 1.5 1.6 1.7

0.7 0.7 0.7 0.7 0.7 0.7 0.7

0.8 0.8 0.9 0.9 1.1 1.2 1.3

Notes:

[7]The array distributed networks consist of 40 half columns and the global distributed networks consist of 44

half columns, each driven by an independent buffer. The number of half columns used does not affect

clock buffer delay. The array clock has up to 8 loads per half column. The global clock has up to 11 loads

per half column.

6-40

40

Preliminary