DP80C51 查看數據表(PDF) - Digital Core Design

零件编号

产品描述 (功能)

生产厂家

DP80C51 Datasheet PDF : 10 Pages

| |||

In most cases the proper number of Wait-

States cycles is between 2-5. The READY pin

can be also dynamically modulated e.g. by

SDRAM controller.

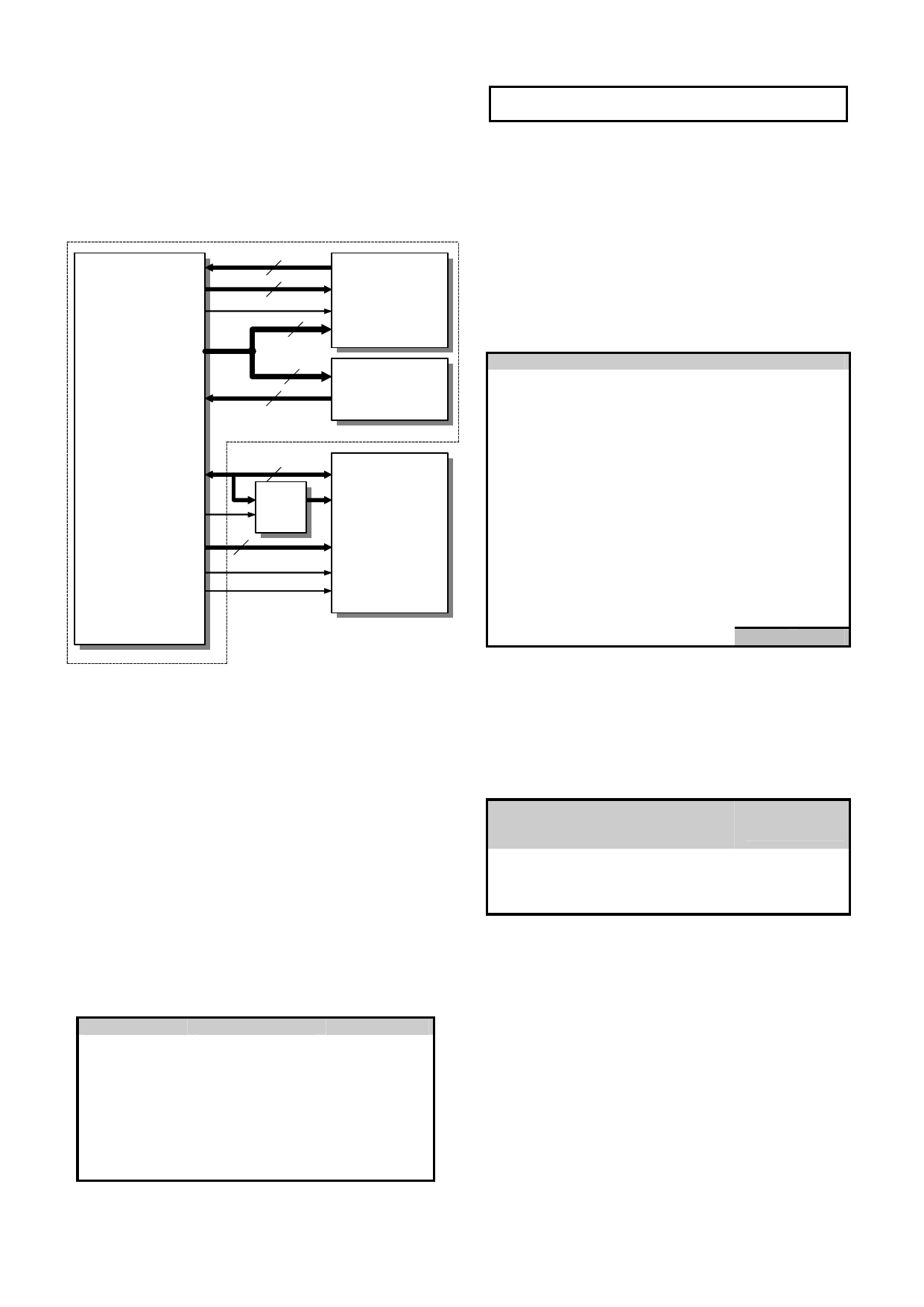

The figure below shows a typical Program

Memories connections in system with

DP80C51 Microcontroller core.

prgramdatai

prgdatao

prgramwr

prgaddr

prgromdatai

DP80C51

8

8

12

On-chip Memory

(implemented as RAM)

0 Wait-State access

10

8

ASIC or FPGA

chip

On-chip Memory

(implemented as ROM)

0 Wait-State access

port0

ale

port2

psen

pswr

8

Latch

8

Off-chip Memory

(implemented as

FLASH, or SRAM)

eg. 2-5 Wait-State

access

STRATIX

-5

90 MHz

STRATIX-II

-3

160 MHz

Core performance in ALTERA® devices

For a user the most important is application

speed improvement. The most commonly used

arithmetic functions and theirs improvement

are shown in table below. Improvement was

computed as {80C51 clock periods} divided by

{DP80C51 clock periods} required to execute

an identical function for code executed from

internal (first column) and external (second

column) program memory. More details are

available in core documentation.

Function

8-bit addition (immediate data)

8-bit addition (direct addressing)

8-bit addition (indirect addressing)

8-bit addition (register addressing)

8-bit subtraction (immediate data)

8-bit subtraction (direct addressing)

8-bit subtraction (indirect addressing)

8-bit subtraction (register addressing)

8-bit multiplication

8-bit division

16-bit addition

16-bit subtraction

16-bit multiplication

32-bit addition

32-bit subtraction

32-bit multiplication

Average speed improvement:

Improvement

9,00 3,00

9,00 3,00

9,00 3,60

12,00 4,00

9,00 3,00

9,00 3,00

9,00 3,60

12,00 4,00

16,00 6,00

9,60 4,80

12,00 4,00

12,00 4,00

13,60 5,47

12,00 4,00

12,00 4,00

12,60 4,89

11,12 4,03

The described above implementation should be

treated as an example. All Program Memory

spaces are fully configurable. For timing-critical

applications whole program code can be imple-

mented as on-chip ROM and (or) RAM and

executed without Wait-States, but for some

other applications whole program code can be

implemented as off-chip ROM or FLASH and

executed with required number Wait-State cy-

cles.

PERFORMANCE

The following tables give a survey about the

Core area and performance in Programmable

Logic Devices after Place & Route (CPU fea-

tures and peripherals have been included):

Device

FLEX10KE

ACEX1K

APEX20K

APEX20KE

APEX20KC

APEX-II

MERCURY

CYCLONE

CYCLONE-II

Speed grade

-1

-1

-1

-1

-7

-7

-5

-6

-6

Fmax

57 MHz

57 MHz

50 MHz

66 MHz

78 MHz

76 MHz

100 MHz

91 MHz

93 MHz

All trademarks mentioned in this document

are trademarks of their respective owners.

Dhrystone Benchmark Version 2.1 was used to

measure Core performance. The following ta-

ble gives a survey about the DP80C51 per-

formance in terms of Dhrystone/sec and VAX

MIPS rating for testing code executed from

external (1) and internal (2) program memory.

Device

Target

Clock

fre-

quency

Dhry/sec

(VAX MIPS)

80C51

-

12 MHz 268 (0.153)

80C310

DP80C511

DP80C512

-

STRATIX-II

STRATIX-II

33 MHz 1550 (0.882)

150 MHz 11525 (6,563)

150 MHz 26220 (14.924)

Core performance in terms of Dhrystones

http://www.DigitalCoreDesign.com

http://www.dcd.pl

Copyright 1999-2007 DCD – Digital Core Design. All Rights Reserved.