DS1742(2008) 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

DS1742 Datasheet PDF : 16 Pages

| |||

DS1742

CLOCK OPERATIONS—READING THE CLOCK

While the double-buffered register structure reduces the chance of reading incorrect data,

internal updates to the DS1742 clock registers should be halted before clock data is read to

prevent reading of data in transition. However, halting the internal clock register updating

process does not affect clock accuracy. Updating is halted when a 1 is written into the read bit,

bit 6 of the century register, see Table 2. As long as a 1 remains in that position, updating is

halted. After a halt is issued, the registers reflect the count, that is day, date, and time that was

current at the moment the halt command was issued. However, the internal clock registers of

the double-buffered system continue to update so that the clock accuracy is not affected by the

access of data. All of the DS1742 registers are updated simultaneously after the internal clock

register updating process has been re-enabled. Updating is within a second after the read bit is

written to 0. The READ bit must be a zero for a minimum of 500μs to ensure the external

registers will be updated.

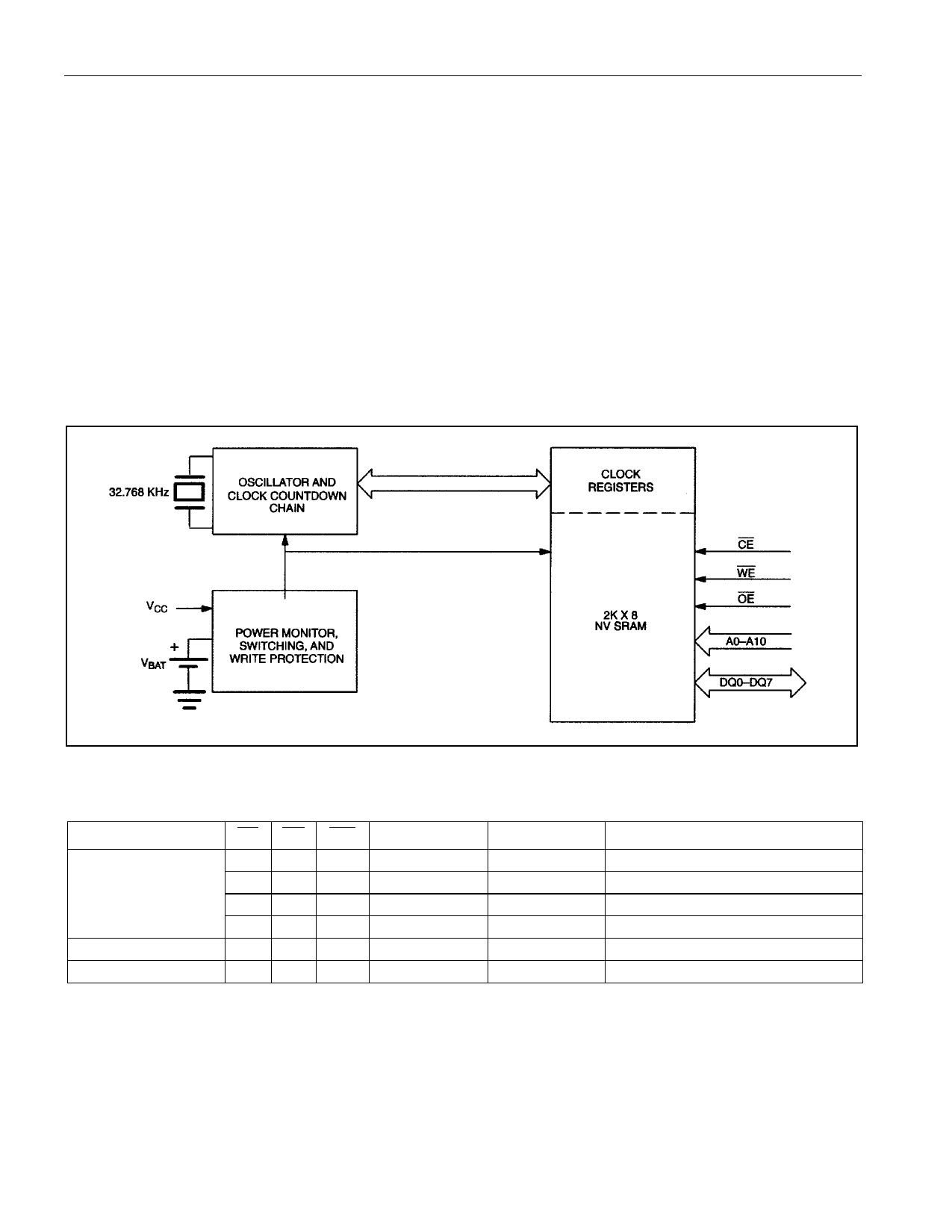

Figure 1. DS1742 BLOCK DIAGRAM

Table 1. TRUTH TABLE

VCC

CE OE WE

VIH X X

VCC > VPF

VIL X VIL

VIL VIL VIH

VIL VIH VIH

VSO < VCC < VPF X X X

VCC < VSO < VPF X X X

MODE

Deselect

Write

Read

Read

Deselect

Deselect

DQ

High-Z

Data In

Data Out

High-Z

High-Z

High-Z

POWER

Standby

Active

Active

Active

CMOS Standby

Data Retention Mode

3 of 16