DS17285S-3 查看數據表(PDF) - Maxim Integrated

零件编号

产品描述 (功能)

生产厂家

DS17285S-3 Datasheet PDF : 30 Pages

| |||

Real-Time Clocks

(VCC = +3.3V, TA = +25°C, unless otherwise noted.)

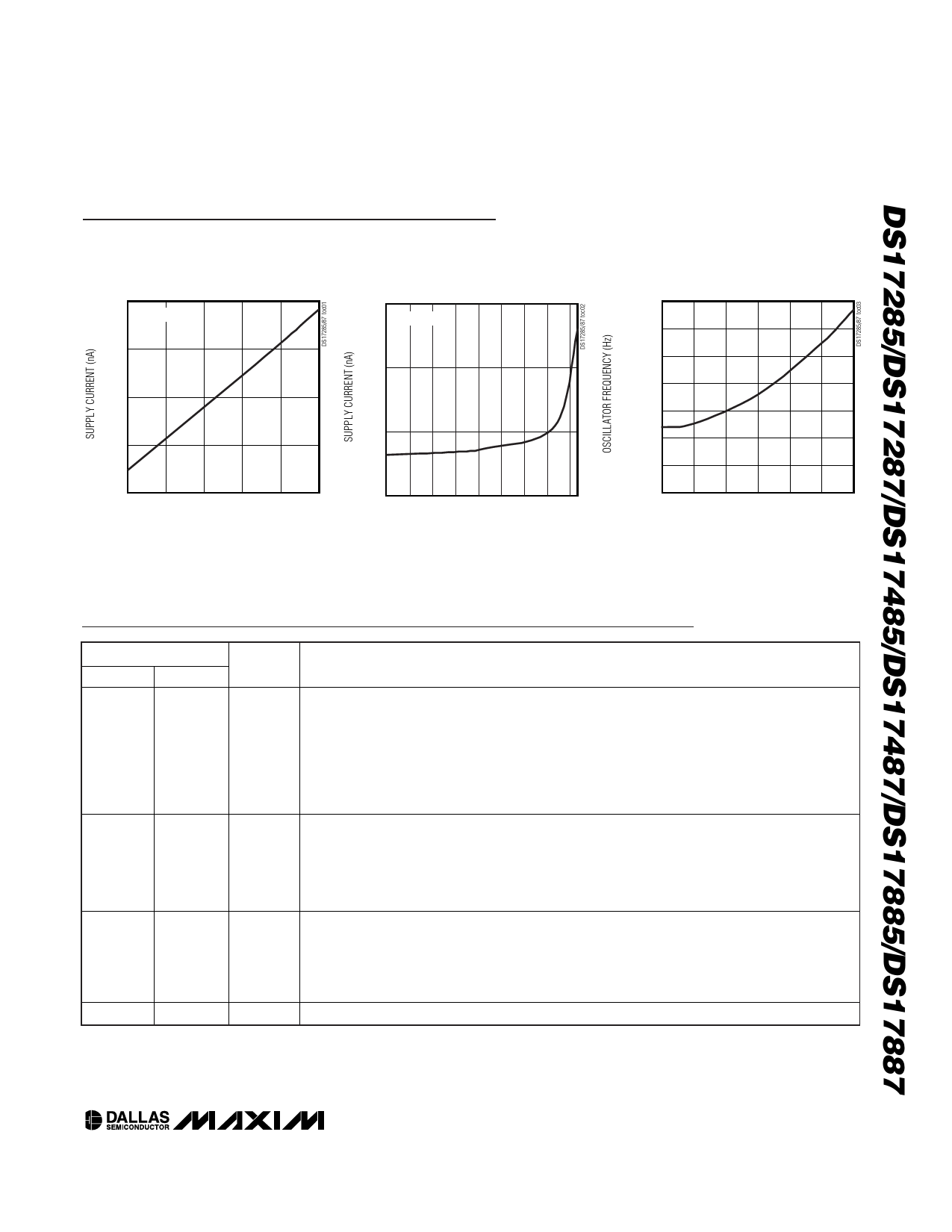

Typical Operating Characteristics

SUPPLY CURRENT

vs. INPUT VOLTAGE

400

VCC = 0V

350

300

250

SUPPLY CURRENT

vs. TEMPERATURE

400

VBAT = 3.0V

350

300

200

2.5 2.8 3.0 3.3 3.5 3.8

VBAT (V)

250

-40 -25 -10 5 20 35 50 65 80

TEMPERATURE (°C)

32768.7

OSCILLATOR FREQUENCY

vs. SUPPLY VOLTAGE

32768.6

32768.5

32768.4

32768.3

32768.2

32768.1

32768.0

2.5 3.0 3.5 4.0 4.5 5.0 5.5

SUPPLY VOLTAGE (V)

Pin Description

PIN

24

28

1

8

NAME

FUNCTION

PWR

Active-Low Power-On Reset. This open-drain output pin is intended for use as an on/off control

for the system power. With VCC voltage removed from the device, PWR can be automatically

activated from a kickstart input by the KS pin or from a wake-up interrupt. Once the system is

powered on, the state of PWR can be controlled by bits in the control registers. The PWR pin

can be connected through a pullup resistor to a positive supply. For 5V operation, the voltage

of the pullup supply should be no greater than 5.7V. For 3V operation, the voltage on the

pullup supply should be no greater than 3.9V.

Connections for Standard 32.768kHz Quartz Crystal. The internal oscillator circuitry is

designed for operation with a crystal having a specified load capacitance (CL) of 6pF or

2, 3

9, 10

X1, X2 12.5pF. Pin X1 is the input to the oscillator and can optionally be connected to an external

32.768kHz oscillator. The output of the internal oscillator, pin X2, is floated if an external

oscillator is connected to pin X1. These pins are missing (N.C.) on the EDIP package.

4–11

12, 16

12–17,

19, 20

AD0–AD7

Multiplexed Bidirectional Address/Data Bus. The addresses are presented during the first

portion of the bus cycle and latched into the device by the falling edge of ALE. Write data is

latched by the rising edge of WR. In a read cycle, the device outputs data during the latter

portion of the RD low. The read cycle is terminated and the bus returns to a high-impedance

state as RD transitions high.

21, 22, 26 GND Ground

_____________________________________________________________________ 7