DSP56303 查看數據表(PDF) - Freescale Semiconductor

零件编号

产品描述 (功能)

生产厂家

DSP56303 Datasheet PDF : 292 Pages

| |||

DSP56303 Overview

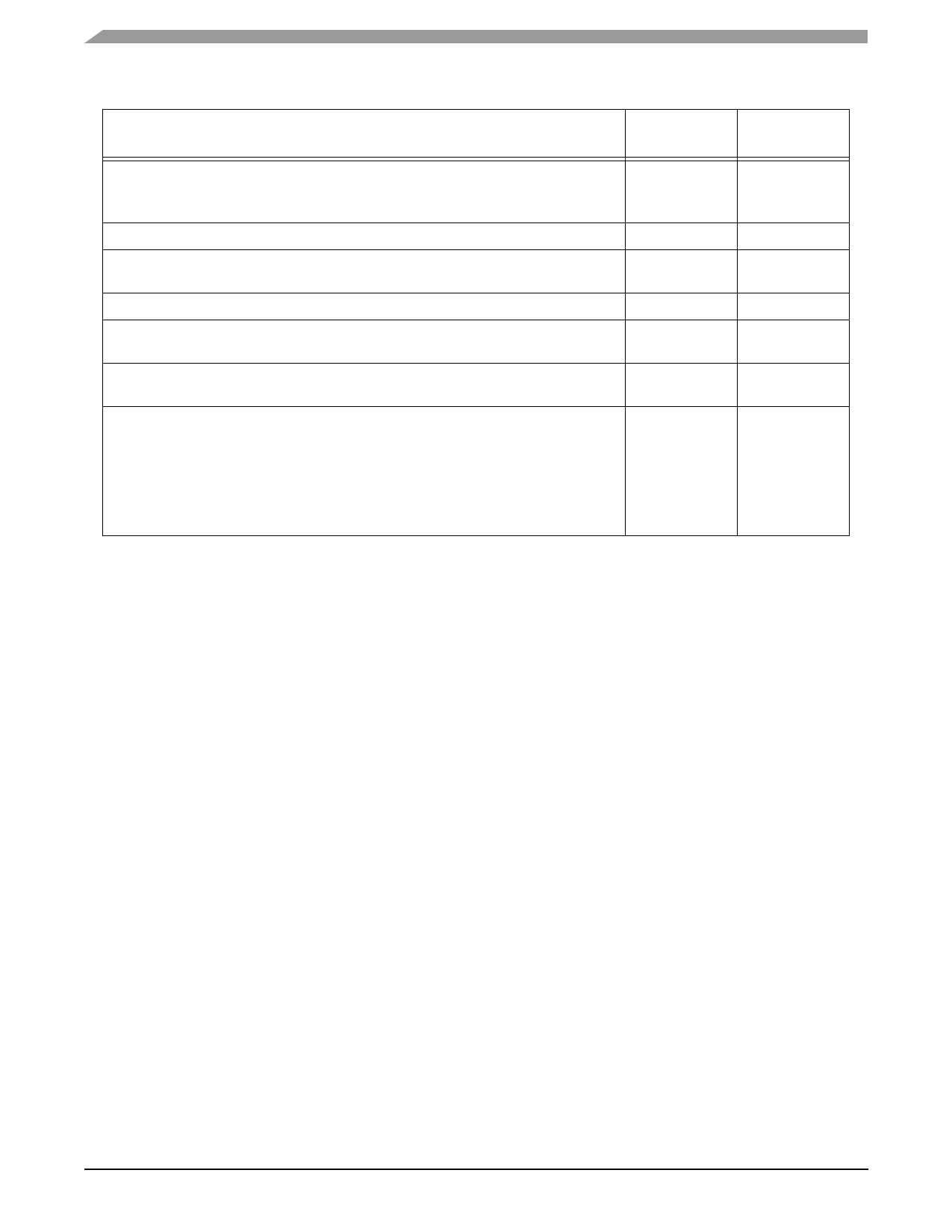

Table 1-2. Change History, Revision 1 to Revision 2 (Continued)

Change

Revision 1

Revision 2

Page Number Page Number

Modified signal definitions. In Table 2-12, deleted the Stop column. Changed the

title of the third column to State During Reset1,2 Added a new note 1 and

changed the old note 1 to note 2.

Operating Mode Register layout and definition. Replaced Figure 4-2.

Operating Mode Register layout and definition. In Table 4-3, changed the

definition for bit 7. Specifically, changed the third line in Note 1.

Bus Control Register (BCR) layout and definition. Replaced Figure 4-6.

Bus Control Register (BCR) layout and definition. In Table 4-8, changed the row

contents for bit 22 to “Reserved. Write to 0 for future compatibility.”

In Section 8.6.4.1, changed the beginning of the fourth paragraph from “In

Synchronous mode” to “In Asynchronous mode.”

Updated programming sheets. Replaced the programming sheets for the following

registers:

• Figure B-2, Operating Mode Register (OMR)

• Figure B-6, Bus Control Register (BCR)

• Figure B-8, Address Attribute Registers (AAR[3–0])

• Figure B-22, Timer Load, Compare, and Count Registers (TLR, TCPR, and

TCR)

Page 2-15 to

2-16

Page 4-15

Page 4-17

Page 4-25

Page 4-26

Page 8-23

Page B-13

Page B-17

Page B-19

Page B-33

Page 2-13 to

2-15

Page 4-13

Page 4-16

Page 4-23

Page 4-23

Page 8-21

Page B-11

Page B-16

Page B-18

Page B-30

1.4 Features

The Freescale DSP56303, a member of the DSP56300 core family of programmable DSPs,

supports wireless infrastructure applications with general filtering operations. Like the other

family members, the DSP56303 uses a high-performance, single-clock-cycle- per-instruction

engine (code compatible with Freescale’s popular DSP56000 core family), a barrel shifter, 24-bit

addressing, instruction cache, and DMA controller. The DSP56303 offers 100 million

instructions per second (MIPS) performance using an internal 100 MHz clock with 3.3 V core

and input/output (I/O) power.

All DSP56300 core family members contain the DSP56300 core and additional modules. The

modules are chosen from a library of standard predesigned elements, such as memories and

peripherals. New modules can be added to the library to meet customer specifications. A standard

interface between the DSP56300 core and the internal memory and peripherals supports a wide

variety of memory and peripheral configurations. In particular, the DSP56303 includes a JTAG

port integrated with the Freescale OnCE™ module.

The DSP56303 is intended for use in telecommunication applications, such as multi-line

voice/data/fax processing, video conferencing, audio applications, control, and general digital

signal processing

DSP56303 User’s Manual, Rev. 2

1-4

Freescale Semiconductor